Daniel José Freire de Araújo

## **Verificação de Refinamento em Diagramas de Sequência com Estruturas de Controle**

Recife

2019

Daniel José Freire de Araújo

## **Verificação de Refinamento em Diagramas de Sequência com Estruturas de Controle**

Monografia apresentada ao Curso de Bacharelado em Ciências da Computação da Universidade Federal Rural de Pernambuco, como requisito parcial para obtenção do título de Bacharel em Ciências da Computação.

Universidade Federal Rural de Pernambuco – UFRPE

Departamento de Computação

Curso de Bacharelado em Ciências da Computação

Orientador: Lucas Albertins de Lima

Recife

2019

MINISTÉRIO DA EDUCAÇÃO E DO DESPORTO

UNIVERSIDADE FEDERAL RURAL DE PERNAMBUCO (UFRPE)

BACHARELADO EM CIÊNCIA DA COMPUTAÇÃO

<http://www.bcc.ufrpe.br>

**FICHA DE APROVAÇÃO DO TRABALHO DE CONCLUSÃO DE CURSO**

Trabalho defendido por **DANIEL JOSÉ FREIRE DE ARAÚJO** às 10:00 do dia 06 de dezembro de 2019, no Auditório do Departamento de Computação - DC – Sala 07, como requisito para conclusão do curso de Bacharelado em Ciência da Computação da Universidade Federal Rural de Pernambuco, intitulado "**Verificação de Refinamento em Diagramas de Sequência com Estruturas de Controle**", orientado por Lucas Albertins de Lima e aprovado pela seguinte banca examinadora:

---

Lucas Albertins de Lima

DC/UFRPE

---

Sidney de Carvalho Nogueira

DC/UFRPE

Dados Internacionais de Catalogação na Publicação

Universidade Federal Rural de Pernambuco

Sistema Integrado de Bibliotecas

Gerada automaticamente, mediante os dados fornecidos pelo(a) autor(a)

---

A663v Araújo, Daniel José Freire de

Verificação de Refinamento em Diagramas de Sequência com Estruturas de Controle / Daniel José Freire de Araújo. - 2019.

70 f. : il.

Orientador: Lucas Albertins de Lima.

Inclui referências.

Trabalho de Conclusão de Curso (Graduação) - Universidade Federal Rural de Pernambuco, Bacharelado em Ciência da Computação, Recife, 2019.

1. UML. 2. Diagrama de Sequência. 3. Refinamento. 4. Estruturas de Controle. I. Lima, Lucas Albertins de, orient.

II. Título

---

CDD 004

# Agradecimentos

Agradeço primeiramente a meus pais pelo amor, apoio e incentivo nas horas difíceis, de desânimo e cansaço.

Ao meu orientador, que sempre mostrou confiança em mim. Obrigado pelo convite para iniciação científica, pela orientação e dedicação à elaboração deste trabalho.

A esta universidade, seu corpo docente, direção e administração que oportunizaram a janela que hoje vislumbro.

Aos meus amigos, companheiros de trabalhos e irmãos na amizade que fizeram parte da minha formação e que vão continuar presentes em minha vida com certeza.

A todos que direta ou indiretamente fizeram parte da minha formação, o meu muito obrigado.

*“A persistência é o caminho do êxito.”*

*(Charles Chaplin)*

# Resumo

A linguagem UML oferece diversos tipos de diagramas para modelagem de sistemas, entre os principais diagramas comportamentais está o diagrama de sequência. O diagrama de sequência pode ser utilizado para modelar casos de uso de sistemas de forma simples e visual. Contudo, a linguagem UML como um todo apresenta modelos informais que possuem verificações baseadas em experiência humana. Este trabalho é a continuação de um linha de pesquisa que tem o objetivo de formalizar diagramas de sequência UML e realizar verificações de refinamento entre diagramas. Aqui é proposta a versão inicial de uma ferramenta capaz de traduzir diagramas de sequência UML para uma especificação formal CSP e realizar a verificação de refinamentos através do verificador FDR4. O ponto diferencial deste trabalho é o processo de formalização de fragmentos combinados que representam estruturas de controle no contexto de diagramas de sequência, aqui serão abordados os fragmentos *option*, *alternative*, *parallel* e *loop*.

**Palavras-chave:** UML, Diagrama de Sequência, Formal, CSP, FDR, Refinamento, Estruturas de Controle, Fragmento Combinado.

# Abstract

The UML language offers several types of diagrams for system modeling, among the main behavioral diagrams is the sequence diagram. The sequence diagram can be used to model system use cases simply and visually. However, the UML language as a whole presents informal models that can only be verified by human experience. This paper refers to the continuation of a research line that aims to formalize UML sequence diagrams and perform refinement checks between diagrams. Here we propose an initial version of a tool capable of translating UML sequence diagrams into CSP and performing a refinement check using the FDR4 verifier. The differential point of this work is the process of formalization of combined fragments that represent control structures in sequence diagrams, here we will cover fragments such as *option, alternative, parallel and loop*.

**Keywords:** UML, Sequence Diagram, Formal, CSP, FDR, Refinement, Control Structure ,Combined Fragment

# Lista de ilustrações

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| Figura 1 – Diagrama de sequência simples                                    | 13 |

| Figura 2 – Linhas de vida de um diagrama de sequência                       | 19 |

| Figura 3 – Mensagens em um diagrama de sequência                            | 20 |

| Figura 4 – Fragmento <i>alt</i>                                             | 21 |

| Figura 5 – Fragmento <i>opt</i>                                             | 22 |

| Figura 6 – Fragmento <i>par</i>                                             | 23 |

| Figura 7 – Diagrama com fragmentos <i>loop</i>                              | 24 |

| Figura 8 – Exemplo de escolha externa                                       | 26 |

| Figura 9 – Visão Geral do Processo de Verificação de Refinamento            | 31 |

| Figura 10 – Exemplo do <i>MessagesBuffer</i>                                | 32 |

| Figura 11 – Diagrama de sequência para tradução                             | 33 |

| Figura 12 – Elementos utilizados na definição de tipos de dados             | 34 |

| Figura 13 – Tipos de dados traduzidos para CSP                              | 34 |

| Figura 14 – Elementos utilizados na definição de canais                     | 36 |

| Figura 15 – Canais CSP                                                      | 36 |

| Figura 16 – Elementos utilizado na definição dos processos de linha de vida | 37 |

| Figura 17 – Processos de linhas de vida em CSP                              | 37 |

| Figura 18 – Processos de mensagens em CSP                                   | 39 |

| Figura 19 – Processo <i>MessagesBuffer</i>                                  | 39 |

| Figura 20 – Diagrama com fragmento <i>alt</i>                               | 40 |

| Figura 21 – Tradução do fragmento <i>alt</i>                                | 41 |

| Figura 22 – Tradução de linhas de vida com fragmento <i>alt</i>             | 42 |

| Figura 23 – Diagrama com fragmento <i>opt</i>                               | 42 |

| Figura 24 – Tradução do fragmento <i>opt</i>                                | 43 |

| Figura 25 – Tradução de linhas de vida com o fragmento <i>opt</i>           | 43 |

| Figura 26 – Tradução do fragmento <i>par</i>                                | 44 |

| Figura 27 – Diagrama com fragmento <i>par</i>                               | 44 |

| Figura 28 – Tradução de linhas de vida com o fragmento <i>par</i>           | 44 |

| Figura 29 – Diagrama de sequência com todos os casos de <i>loop</i>         | 45 |

| Figura 30 – Processo auxiliar do <i>loop</i> com um limite                  | 46 |

| Figura 31 – Processo auxiliar do <i>loop</i> com dois limites               | 46 |

| Figura 32 – Processo auxiliar do <i>loop</i> infinito                       | 47 |

| Figura 33 – Tradução de linhas de vida com <i>loop</i>                      | 47 |

| Figura 34 – Processo <i>SeqParallel</i>                                     | 47 |

| Figura 35 – Processo final do diagrama exemplo                              | 48 |

| Figura 36 – Configuração de refinamento da ferramenta                       | 50 |

|                                                                                       |    |

|---------------------------------------------------------------------------------------|----|

| Figura 37 – Rastreabilidade de contraexemplo na ferramenta . . . . .                  | 51 |

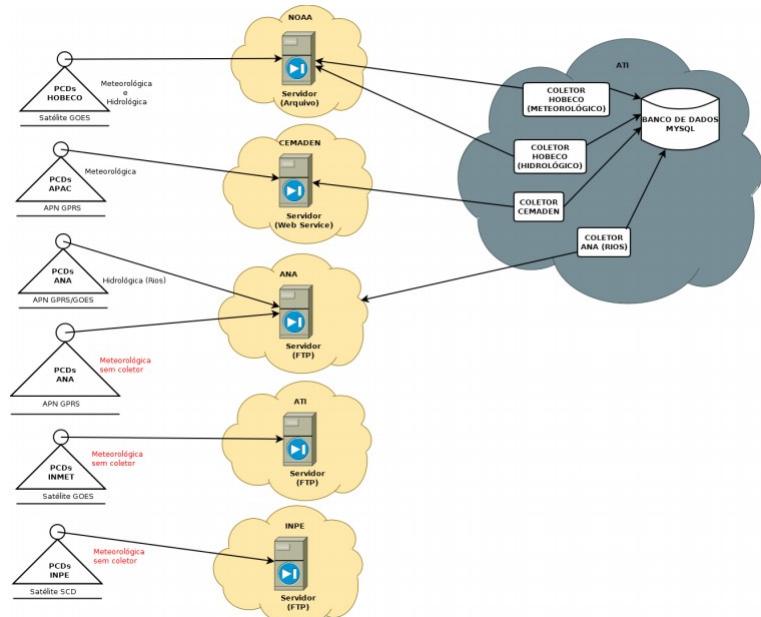

| Figura 38 – Arquitetura de coleta de dados da APAC . . . . .                          | 53 |

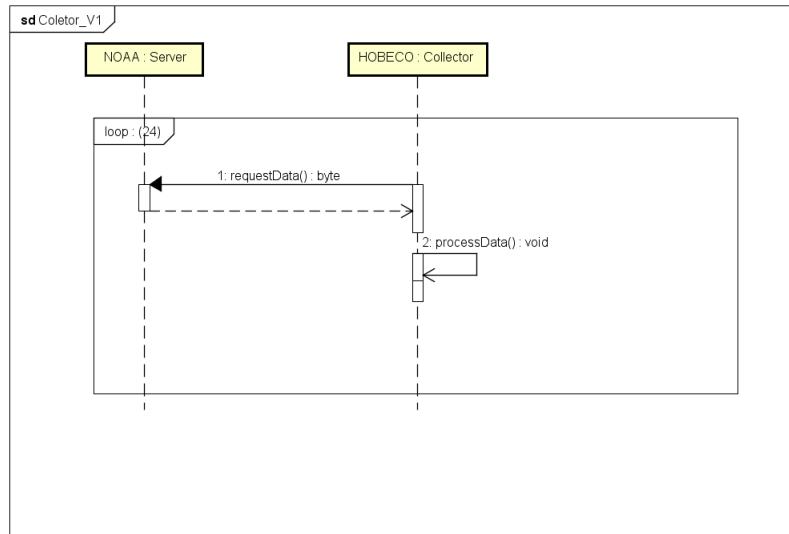

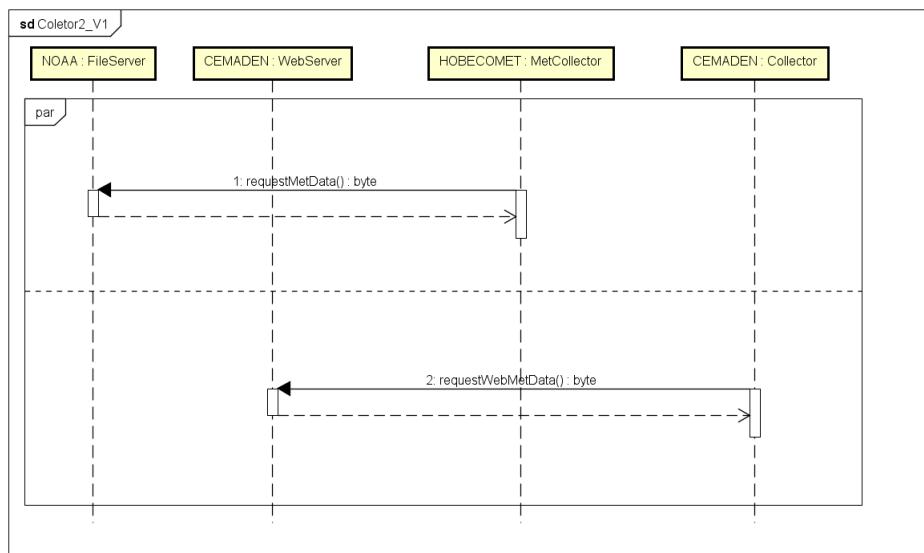

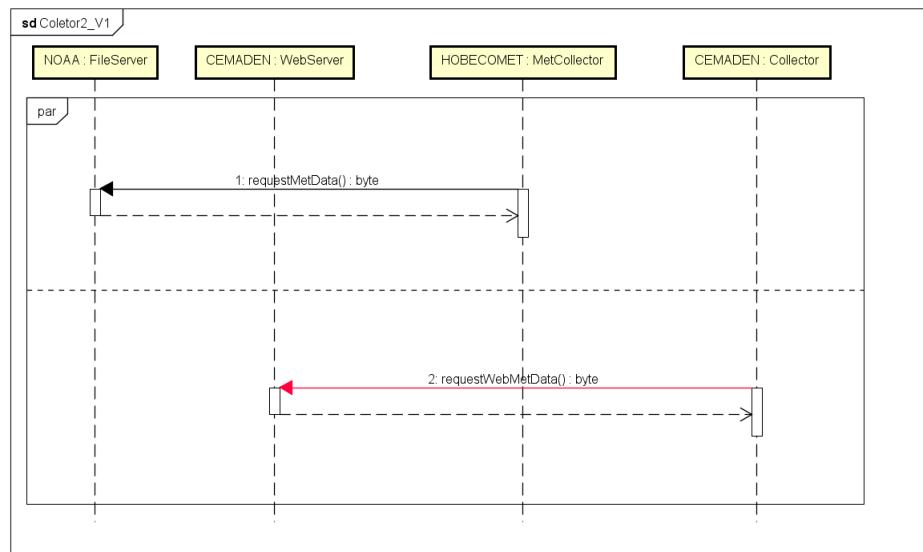

| Figura 39 – Modelagem inicial da coleta de dados . . . . .                            | 55 |

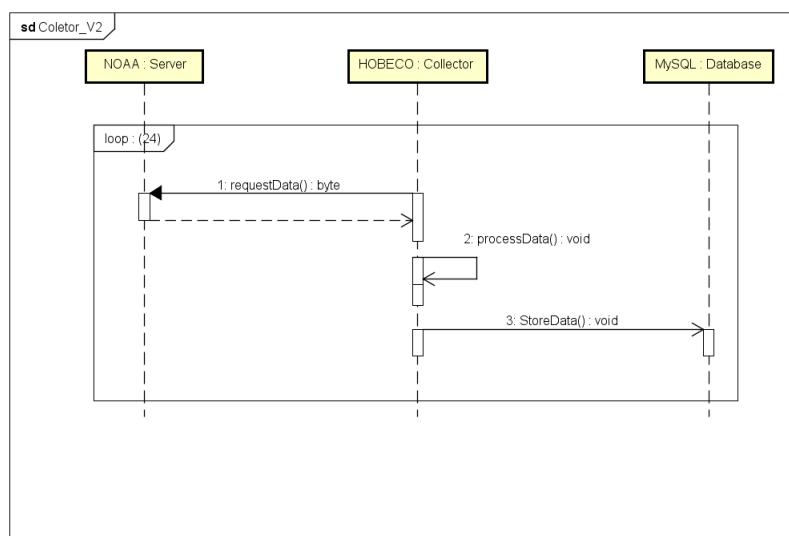

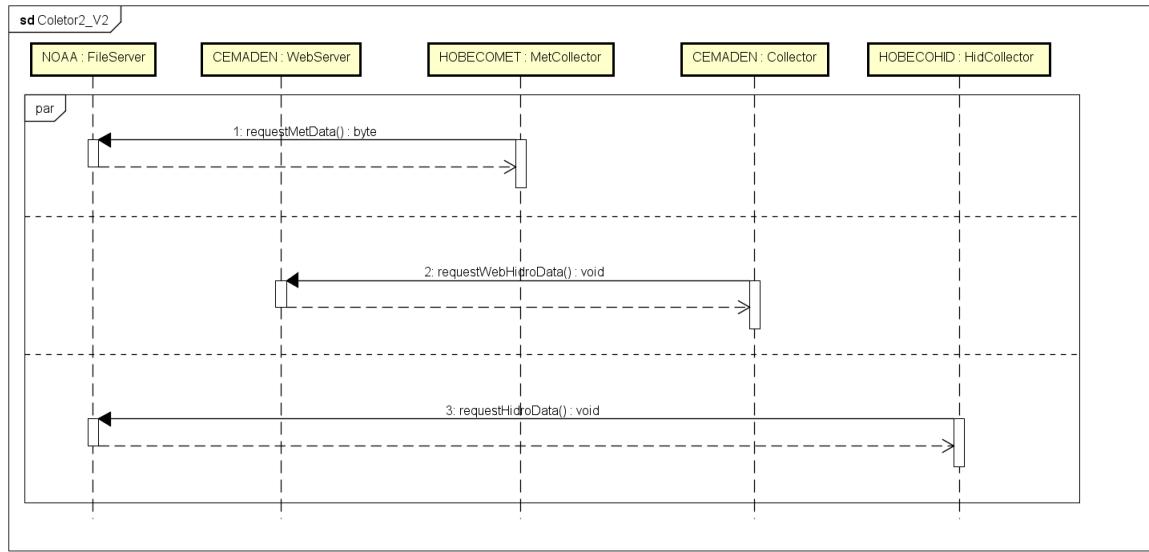

| Figura 40 – Modelagem atualizada da coleta de dados . . . . .                         | 55 |

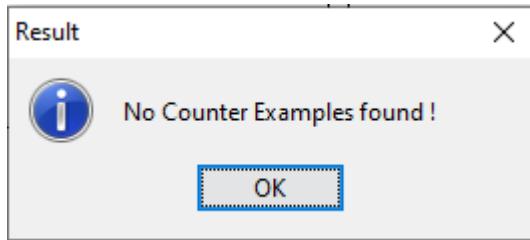

| Figura 41 – Confirmação da verificação de refinamento . . . . .                       | 56 |

| Figura 42 – Modelagem inicial da coleta de dados por múltiplos coletores . . . . .    | 56 |

| Figura 43 – Modelagem atualizada da coleta de dados por múltiplos coletores . . . . . | 57 |

| Figura 44 – Contraexemplo da modelagem de múltiplos coletores . . . . .               | 57 |

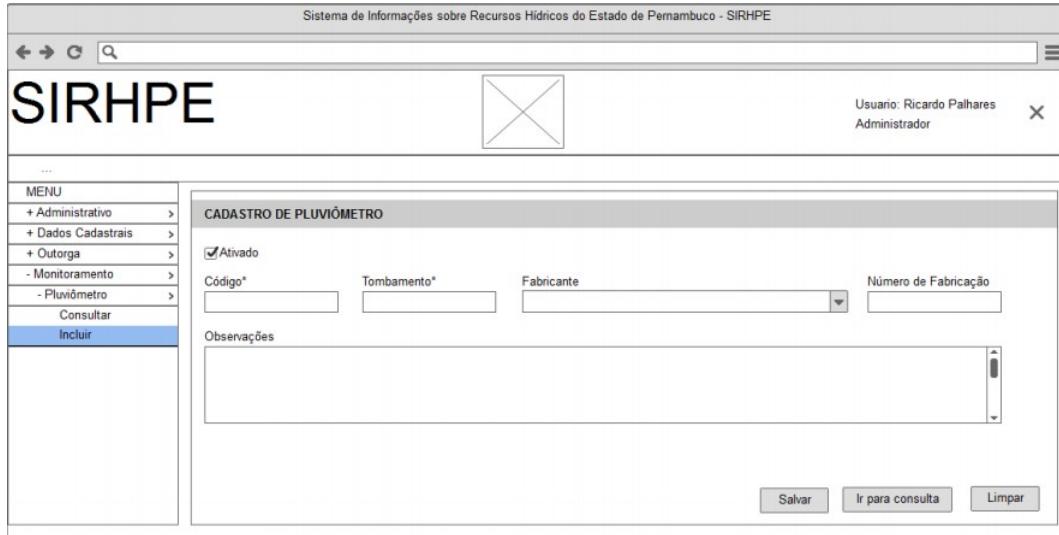

| Figura 45 – Protótipo de interface para adição de pluviômetro no SIRHPE . . . . .     | 59 |

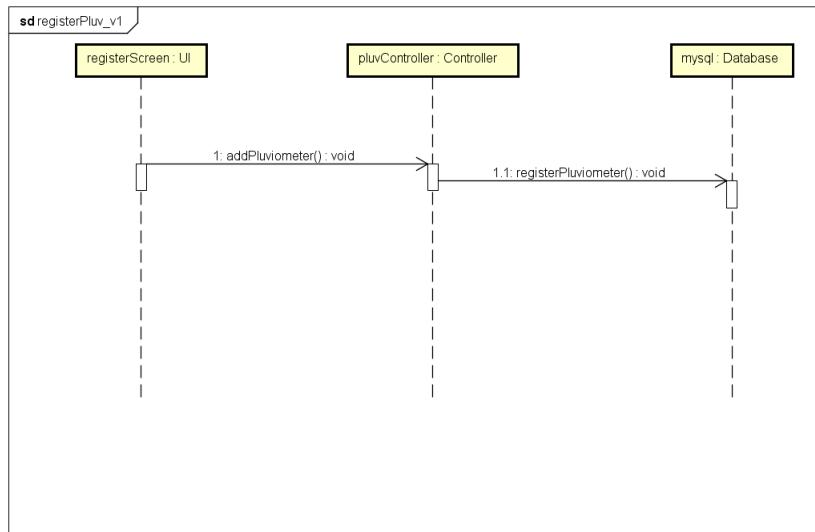

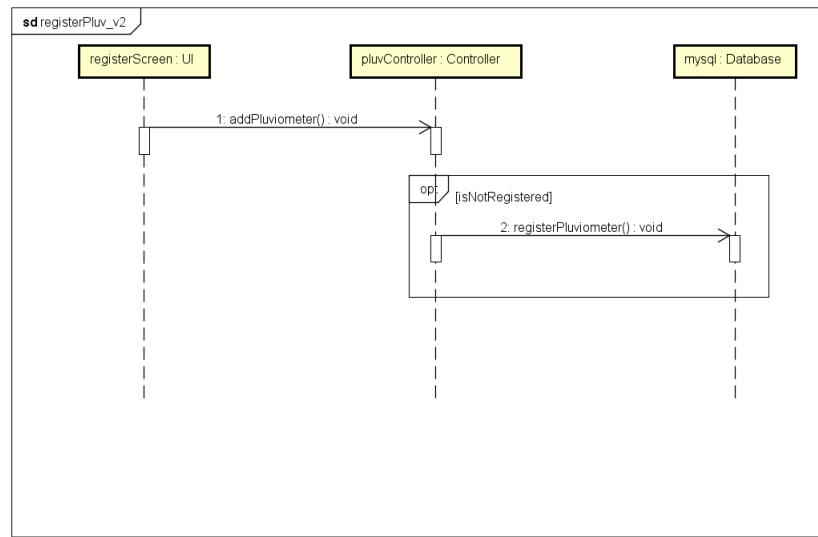

| Figura 46 – Modelagem inicial da adição de novo pluviômetro . . . . .                 | 59 |

| Figura 47 – Modelagem atualizada da adição de novo pluviômetro . . . . .              | 60 |

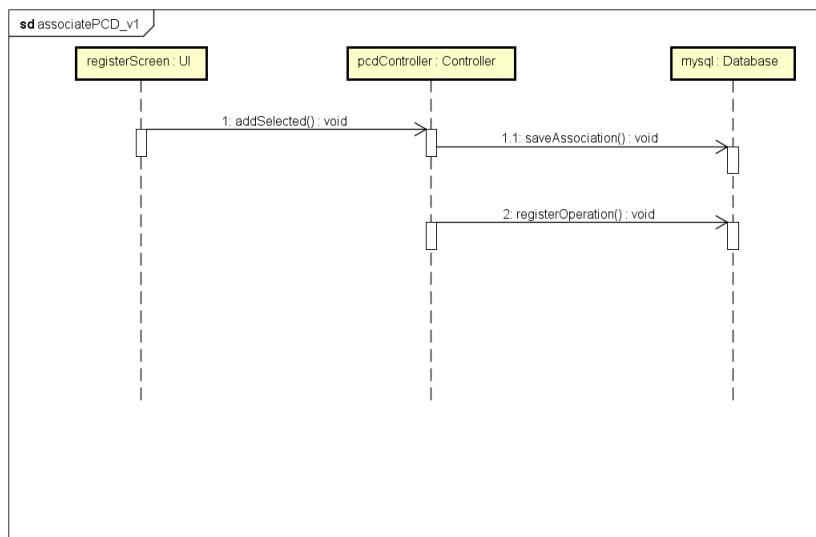

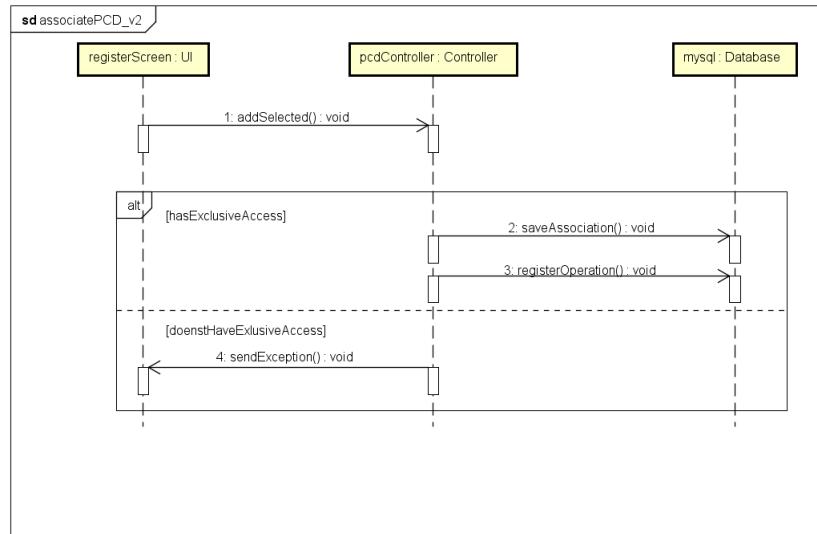

| Figura 48 – Modelagem inicial da associação de periférico à PCD . . . . .             | 61 |

| Figura 49 – Modelagem atualizada da associação de periféricos à PCD . . . . .         | 62 |

# Lista de tabelas

|                                                                     |    |

|---------------------------------------------------------------------|----|

| Tabela 1 – Tabela de comparação de trabalhos relacionados . . . . . | 65 |

|---------------------------------------------------------------------|----|

# **Lista de abreviaturas e siglas**

|         |                                                                  |

|---------|------------------------------------------------------------------|

| UML     | Unified Modeling Language                                        |

| CSP     | Communicating Sequential Processes                               |

| OCL     | Object Constraint Language                                       |

| APAC    | Agência Pernambucana de Águas e clima                            |

| SIRHPE  | Sistema de Informação para Recursos Hídricos de Pernambuco       |

| PCD     | Plataforma de Coleta de Dados                                    |

| CEMADEN | Centro Nacional de Monitoramento e Alertas de Desastres Naturais |

| INPE    | Instituto Nacional de Pesquisas Espaciais                        |

| CPTEC   | Centro de Previsão de Tempo e Estudos Climáticos                 |

# Sumário

|                             |                                                             |           |

|-----------------------------|-------------------------------------------------------------|-----------|

| <b>Lista de ilustrações</b> | <b>6</b>                                                    |           |

| <b>1</b>                    | <b>INTRODUÇÃO</b>                                           | <b>12</b> |

| 1.1                         | Contexto da Pesquisa                                        | 12        |

| 1.2                         | Problema da pesquisa                                        | 13        |

| 1.3                         | Justificativa                                               | 14        |

| 1.4                         | Objetivos                                                   | 15        |

| 1.4.1                       | Objetivo Geral                                              | 15        |

| 1.4.2                       | Objetivos Específicos                                       | 15        |

| 1.5                         | Metodologia                                                 | 16        |

| 1.6                         | Estrutura do Trabalho                                       | 16        |

| <b>2</b>                    | <b>FUNDAMENTAÇÃO TEÓRICA</b>                                | <b>18</b> |

| 2.1                         | Diagramas de Sequência                                      | 18        |

| 2.1.1                       | Linhas de vida                                              | 18        |

| 2.1.2                       | Mensagens                                                   | 19        |

| 2.1.3                       | Fragmentos Combinados                                       | 20        |

| 2.1.3.1                     | Alternative - alt                                           | 21        |

| 2.1.3.2                     | Option - opt                                                | 22        |

| 2.1.3.3                     | Parallel - par                                              | 22        |

| 2.1.3.4                     | Loop - loop                                                 | 22        |

| 2.2                         | <b>CSP</b>                                                  | <b>24</b> |

| 2.2.1                       | Processos e eventos                                         | 24        |

| 2.2.2                       | Tipos de dados e Canais                                     | 25        |

| 2.2.3                       | Operadores                                                  | 26        |

| 2.2.3.1                     | Operador prefixo                                            | 26        |

| 2.2.3.2                     | Escolha externa                                             | 26        |

| 2.2.3.3                     | Composição sequencial                                       | 26        |

| 2.2.3.4                     | Entrelaçamento                                              | 27        |

| 2.2.3.5                     | Composição paralela generalizada                            | 27        |

| 2.2.3.6                     | Composição paralela alfabetizada                            | 27        |

| 2.2.3.7                     | Esconder                                                    | 28        |

| 2.2.4                       | Modelo Semânticos e Traces                                  | 28        |

| <b>3</b>                    | <b>VERIFICAÇÃO DE REFINAMENTO DE DIAGRAMAS DE SEQUÊNCIA</b> | <b>30</b> |

|            |                                                              |           |

|------------|--------------------------------------------------------------|-----------|

| <b>3.1</b> | <b>Visão Geral do Processo de Verificação de Refinamento</b> | <b>30</b> |

| <b>3.2</b> | <b>Tradução</b>                                              | <b>31</b> |

| 3.2.1      | Definição de tipos de dados                                  | 33        |

| 3.2.2      | Definição de canais de comunicação                           | 35        |

| 3.2.3      | Construção dos processos de linhas de vida e mensagem        | 37        |

| <b>3.3</b> | <b>Tradução de Fragmentos Combinados</b>                     | <b>39</b> |

| 3.3.1      | Tradução do fragmento alt                                    | 40        |

| 3.3.2      | Tradução do fragmento opt                                    | 41        |

| 3.3.3      | Tradução do fragmento par                                    | 43        |

| 3.3.4      | Tradução do fragmento loop                                   | 43        |

| <b>3.4</b> | <b>Paralelismo e Sincronização</b>                           | <b>47</b> |

| <b>3.5</b> | <b>Verificação de Refinamento</b>                            | <b>48</b> |

| 3.5.1      | Weak Refinement                                              | 50        |

| 3.5.2      | Strict Refinement                                            | 50        |

| <b>3.6</b> | <b>Contraexemplo e Rastreabilidade</b>                       | <b>51</b> |

| <b>4</b>   | <b>AVALIAÇÃO</b>                                             | <b>53</b> |

| <b>4.1</b> | <b>Coletores de dados da APAC</b>                            | <b>53</b> |

| 4.1.1      | Caso 1: Processo de um Coletor                               | 54        |

| 4.1.2      | Caso 2: Processo de múltiplos Coletores                      | 56        |

| <b>4.2</b> | <b>SIRHPE</b>                                                | <b>58</b> |

| 4.2.1      | Caso 1: Adicionar Pluviômetro                                | 58        |

| 4.2.2      | Caso 2: Associar Periférico à PCD                            | 60        |

| <b>5</b>   | <b>CONCLUSÃO</b>                                             | <b>63</b> |

| <b>5.1</b> | <b>Contribuições</b>                                         | <b>63</b> |

| <b>5.2</b> | <b>Trabalhos Relacionados</b>                                | <b>64</b> |

| <b>5.3</b> | <b>Limitações e trabalhos futuros</b>                        | <b>65</b> |

|            | <b>REFERÊNCIAS</b>                                           | <b>67</b> |

# 1 Introdução

Este trabalho se trata da extensão do projeto de iniciação científica intitulado "Desenvolvimento de um Arcabouço para Verificação de Refinamento de Modelos UML Comportamentais".

## 1.1 Contexto da Pesquisa

Um projeto em etapas (*stepwise design*) de um sistema inicia de um modelo abstrato e evolui para um modelo concreto enquanto os conceitos do sistema amadurecem (KHENDEK; BOURDUAS; VINCENT, 2001). Essa tarefa de projetar é comumente realizada através da produção de uma série de modelos de projeto onde cada modelo é um refinamento de um anterior. Durante o processo tradicional de desenvolvimento de software, é comum que se construa uma série de diagramas que representam visualmente a arquitetura ou funcionamento de alguma parte do sistema (SOMMERVILLE, 2011). Nesse contexto, um refinamento entre diagramas representa que um diagrama mais recente preserva propriedades de um diagrama construído previamente, mas adiciona novas características.

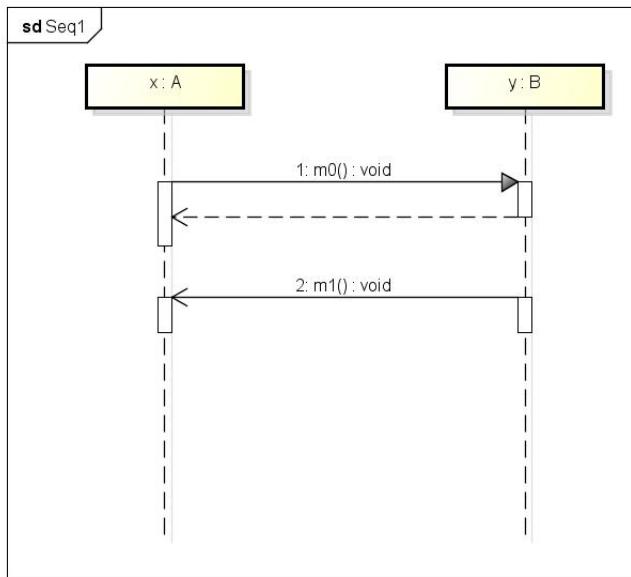

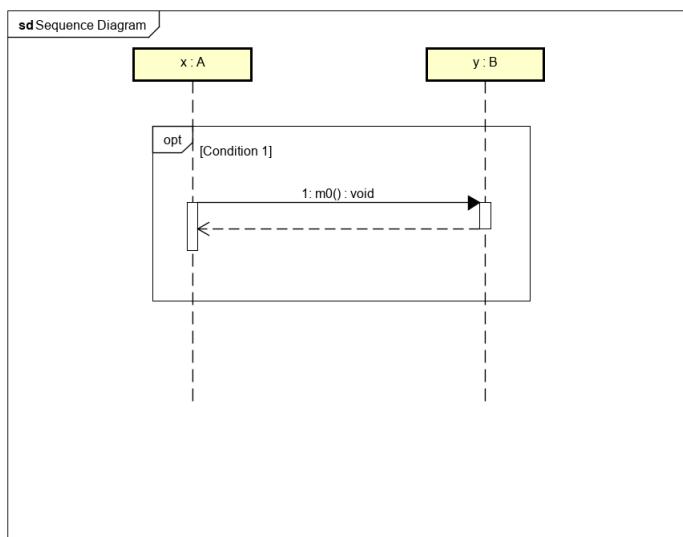

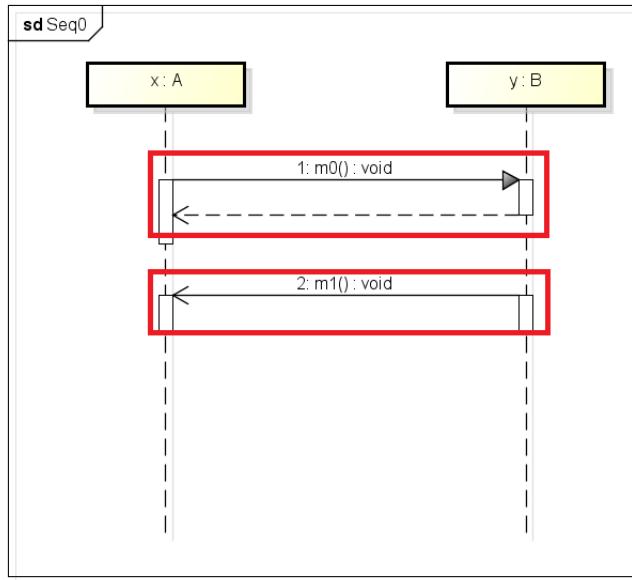

A linguagem UML (UML, 2015) é bastante conhecida como um padrão para se criar modelos de projeto de sistemas, sejam eles de hardware ou de software, ela possui diagramas que possibilitam a modelagem tanto da parte estrutural como também a parte comportamental de sistemas. Dentre os diagramas comportamentais, o diagrama de sequência é comumente utilizado em projetos de software, onde tem o propósito de descrever interações entre diversas entidades do sistema. A Figura 1 ilustra um diagrama de sequência simples.

A imagem ilustra um diagrama com dois objetos, x da classe A e y da classe B. Esses objetos trocam mensagens entre si, tais mensagens são representadas pelas setas e seus respectivos rótulos, m0 e m1. As características do diagrama de sequência e seus componentes serão melhor exploradas no capítulo de Fundamentação Teórica.

Figura 1 – Diagrama de sequência simples

## 1.2 Problema da pesquisa

Modelos de projeto podem ter semânticas informais ou formais, quando falamos de modelos formais no contexto de software é comum que sejam citados um ou mais métodos formais. “Métodos formais utilizados no desenvolvimento de sistema de computadores são técnicas matemáticas para descrever propriedades de um sistema. Tais métodos formais provêm frameworks nos quais as pessoas podem especificar, desenvolver e verificar sistemas de forma sistemática e não ad hoc”(WING, 1990) tradução nossa.

Modelos informais, como os que usam a linguagem UML (KENT; EVANS; RUMPE, 1999), são populares pois permitem representar ideias de forma simples e visual, com poucas regras e limitações preestabelecidas. Tanto nos processos tradicionais quanto nas metodologias ágeis como *Scrum* (SCHWABER; BEEDLE, 2002) e *Extreme Programming* (BECK, 2000), ainda é comum se utilizar diferentes tipos de diagramas UML em projetos de software, seja de forma obrigatória ao processo, visando representar a estrutura de elementos de um sistema, ou de forma complementar para compartilhar o entendimento de um projeto dentro de uma equipe de desenvolvedores.

Os modelos formais por sua vez, são mais complexos devido à necessidade de entendimento e manipulação de conceitos matemáticos e semânticas formais (WINS-KEL, 1993). Esses tipos de modelos não possuem uma aplicação tão comum quanto os modelos informais, e por isso são geralmente utilizados em contextos onde são obrigatórios, como por exemplo em sistemas críticos (STOREY, 1996). De forma geral, os modelos formais são mais seguros pois garantem corretude por prova matemática, além de possuírem diversas regras preestabelecidas que evitam ambiguidades e di-

vergências semânticas. Outro ponto característico de modelos formais é a existência de ferramental para realizar diversos tipos de validações entre seus modelos de forma automatizada.

A verificação de refinamento é um exemplo de verificação que pode ser realizada em modelos formais. Uma verificação de refinamento entre modelos deve verificar se as propriedades definidas em um modelo abstrato estão presentes em um modelo mais concreto, independentemente do modelo concreto possuir novas propriedades. No contexto de diagramas UML, uma verificação de refinamento entre diagramas iria verificar se as propriedades definidas em um diagrama de mais alto nível se mantém em um diagrama de mais baixo nível e com mais detalhes.

Quando um modelo de projeto tem uma semântica informal como no UML, cabe ao projetista julgar se o modelo concreto é um refinamento de um modelo abstrato. O projetista se baseia somente na sua intuição e experiência, as quais podem levar a erros devido ao fator humano. Em projetos de sistemas críticos, onde um erro pode levar a situações desastrosas como grande perda financeira ou perda de vidas humanas, são utilizados modelos com semânticas formais, uma vez que esse tipo de modelo pode ser analisado de forma automática através de ferramentas como verificadores de modelos (BAIER; KATOEN, 2008). Uma inconsistência não detectada nas etapas iniciais de um projeto de software pode resultar em um alto custo para sua correção.

Tendo esses pontos em vista, como poderíamos unir a praticidade de uso dos modelos informais com a segurança e o ferramental presentes em modelos formais para verificar refinamentos em diagramas de sequência UML?

### 1.3 Justificativa

Inicialmente vendida como uma linguagem para especificação de modelos de software orientado a objeto (UML, 2015), hoje a UML é difundida como uma linguagem diagramática de propósito geral extremamente abrangente, com uma série de diagramas para diferentes fins. Entretanto, tal abrangência dificulta o nível de validações que podemos realizar nesses modelos devido a sua semântica informal, a qual é descrita textualmente em linguagem natural.

Com essas características em mente, planejamos realizar uma conversão de UML para a linguagem CSP (HOARE, 1985), com foco nos diagramas de sequência. Ao descrever a semântica de diagramas da linguagem UML usando uma notação como CSP estamos definindo uma semântica formal para um modelo informal. Dessa forma, além de poder definir modelos não ambíguos, podemos usar o poder ferramental de uma linguagem formal para realizar raciocínio lógico automatizado nos modelos.

A notação CSP fornece uma álgebra de processo para especificação de sistemas concorrentes, ela possui uma semântica formal não ambígua e mecanismos de cálculo de refinamento. Além disso possui uma série de operadores que facilitam a definição de uma semântica composicional para os elementos da UML. Possui também modelos semânticos compatíveis com a semântica de diagramas de sequência, a qual é baseada em sequência de eventos, também conhecida como *traces*. Acima de tudo isto possui raciocínio automatizado através da ferramenta FDR ([GIBSON-ROBINSON et al., 2014](#)).

O foco deste trabalho é utilizar verificação de refinamento presente no CSP para melhorar o processo de detecção de inconsistências durante a modelagem de diagramas de sequência de um sistema. Para tanto, vislumbramos adaptar semânticas formais definidas anteriormente em ([LIMA; IYODA; SAMPAIO, 2016](#)).

Tal trabalho serve como base para a criação de uma estratégia de tradução de diagramas de sequência para a notação CSP. Usando a ferramenta FDR conseguimos verificar refinamentos de tais especificações baseando-se nas noções de refinamento de diagrama de sequência definidas em ([LIMA; IYODA; SAMPAIO, 2016](#)). O cenário ideal é unir os dois mundos, onde o projetista pode focar no nível UML e utilizar uma ferramenta formal para realizar verificações de refinamento.

## 1.4 Objetivos

### 1.4.1 Objetivo Geral

Expandir o arcabouço de verificação de refinamento e tradução de diagramas de sequência visando o desenvolvimento de uma ferramenta com foco em minimizar o esforço com validações neste tipo de diagrama e permitir a detecção de falhas de forma antecipada, assim, reduzindo custos.

### 1.4.2 Objetivos Específicos

1. Extender o módulo de tradução de diagramas de sequência desenvolvido em trabalhos anteriores visando dar a suporte a tradução de fragmentos combinados.

2. Extender o módulo de verificação de refinamentos de diagramas de sequência desenvolvido em trabalhos anteriores visando melhorar a rastreabilidade de faixas de refinamento.

3. Desenvolver uma ferramenta no formato de plugin da plataforma Astah ([CHANGE-VISION, 2018](#)), capaz de verificar refinamentos entre diagramas de sequência.

## 1.5 Metodologia

Como citado anteriormente nos objetivos, o desenvolvimento desta pesquisa está atrelado ao desenvolvimento de uma ferramenta no formato de plugin para a plataforma Astah. Todas as etapas de desenvolvimento da ferramenta serão realizadas com a linguagem Java ([GOSLING; HOLMES; ARNOLD, 2005](#)), utilizando como base os diagramas criados na plataforma Astah. Este projeto de pesquisa será desenvolvido seguindo as seguintes etapas:

- 1. Adaptar semântica CSP para tradução de diagramas de sequência:** Nesta pesquisa adaptaremos uma semântica formal definida em trabalhos anteriores, essas adaptações têm o intuito de facilitar a utilização da semântica no contexto de uma ferramenta.

- 2. Desenvolver um tradutor UML → CSP:** Essa é a primeira etapa do desenvolvimento da ferramenta, aqui transformaremos um diagrama de sequência UML em uma especificação CSP com a semântica definida na etapa anterior.

- 3. Integrar verificador FDR à ferramenta:** Após a tradução dos diagramas podemos utilizar as funcionalidades do FDR para realizar verificações de refinamento nas especificações CSP geradas.

- 4. Desenvolver um tradutor de contraexemplos:** Em casos de falha de refinamento, a ferramenta FDR retorna um contraexemplo que identifica onde houve a falha. Para exibir a falha de forma intuitiva precisamos transformá-la em um diagrama de sequência e destacar o elemento que causou a inconsistência.

- 5. Integração da ferramenta como plugin Astah:** Integrar todos os elementos citados anteriormente em uma ferramenta única, no formato de plugin da plataforma Astah.

- 6. Realização de estudos de caso:** Validar a ferramenta criada com diferentes estudos de caso.

## 1.6 Estrutura do Trabalho

Além desse capítulo introdutório, este trabalho apresenta mais quatro capítulos. O Capítulo 2 apresenta o embasamento teórico necessário para o desenvolvimento deste trabalho, nele são contemplados os principais conceitos relacionados a diagramas de sequência e à linguagem CSP.

O Capítulo 3 apresenta os resultados obtidos na pesquisa, exemplificando todo o processo de tradução e seus resultados.

O Capítulo 4 apresenta um estudo de caso da aplicação da ferramenta desenvolvida neste trabalho, nele são contemplados diversos exemplos do uso da ferramenta no contexto de um projeto real.

Por fim, o Capítulo 5 contém a conclusão do trabalho, nele são apresentadas todas as contribuições, limitações e dificuldades do trabalho, além de comentar trabalhos relacionados e possíveis trabalhos futuros na área de pesquisa.

## 2 Fundamentação Teórica

Esse capítulo tem o intuito de apresentar conceitos fundamentais ao desenvolvimento deste trabalho. As seções a seguir irão fornecer o embasamento teórico necessário para o entendimento de diagramas de sequência UML e da linguagem CSP.

A primeira seção aborda os diagramas de sequência, nela serão contemplados todos os elementos de diagramas utilizados neste trabalho. Todos os exemplos serão ilustrados com diagramas construídos na plataforma Astah, que é a plataforma alvo da ferramenta desenvolvida neste trabalho.

A segunda seção aborda a linguagem CSP com foco em seus operadores e modelo de trances, que é o modelo utilizado para verificações. Nela serão contemplados todos os operadores utilizados neste trabalho.

### 2.1 Diagramas de Sequência

A linguagem UML possui uma série de diagramas de diferentes tipos e funções, entre os tipos de diagrama podemos identificar duas grandes categorias: diagramas estruturais e diagramas comportamentais. Nesta pesquisa iremos focar em diagramas de sequência, um dos principais diagramas comportamentais.

Os diagramas comportamentais, assim como sugere sua classificação, tem foco em representar o comportamento de um sistema através da representação de interações. O diagrama de sequência representa a interação entre entidades de um sistema durante sua execução, essas interações são representadas através de trocas de mensagem ao longo do tempo.

A seguir apresentaremos os elementos básicos que compõem um diagrama de sequência. Após a introdução dos elementos básicos iremos apresentar elementos mais complexos que são o foco deste trabalho.

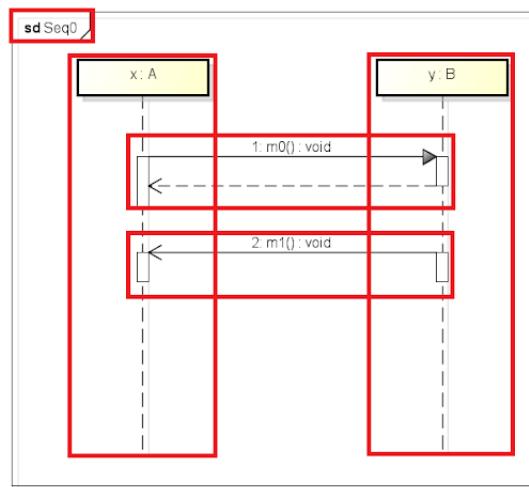

#### 2.1.1 Linhas de vida

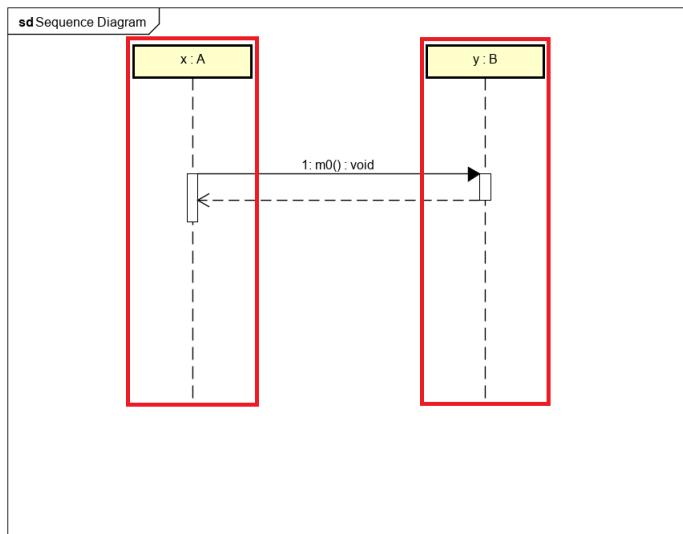

As linhas de vida ou *lifelines* representam as entidades presentes em um diagrama de sequência e suas interações ao longo do tempo. Tais interações são representadas ao longo do eixo vertical de uma linha de vida, esse eixo representa a passagem de tempo, onde o ponto mais alto do eixo representa o inicio da interação e a base do eixo representa o fim da interação. Dependendo do contexto que o diagrama representa, uma linha de vida pode representar diferentes elementos. Considerando o

contexto de um sistema de software, uma linha de vida pode ser utilizada para representar as entidades do sistema, tal como classes e suas respectivas instâncias, além disso também é possível representar elementos mais complexos como um sistema externo ou até mesmo atores do processo representado. Na Figura 2 destacamos as linhas de vida presentes em um diagrama de sequência simples.

Figura 2 – Linhas de vida de um diagrama de sequência

De forma geral podemos afirmar que as linhas de vida representam as entidades que se comunicam no modelo em questão.

### 2.1.2 Mensagens

As mensagens do diagrama de sequência representam a comunicação entre as suas entidades. Toda mensagem deve ligar uma linha de vida a outra ou a ela mesma, e a sua disposição na vertical representa a ordem que irá acontecer. A ordem do envio de mensagens é definida de cima para baixo, sendo a mensagem mais acima a primeira que será enviada. Uma mensagem pode ser dividida em dois eventos: envio e recebimento.

No contexto de um sistema de software as mensagens podem representar a chamadas de função em diferentes entidades do sistema. Um dos conceitos mais importantes da mensagem é o seu significado semântico. As mensagens em diagrama de sequência podem ser representadas de duas formas :

- **Mensagem Síncrona:** Esse tipo de mensagem representa a comunicação síncrona entre linhas de vida, ou seja, em uma mensagem síncrona a linha de vida que envia a mensagem espera uma resposta para continuar sua execução. Esse tipo de mensagem é comumente utilizada para representar chamadas de méth-

dos que possuem algum retorno. O retorno de uma mensagem síncrona é representada na forma de uma mensagem de resposta. Em um diagrama de sequência a mensagem síncrona é representada por uma seta com ponta preenchida, enquanto que a sua mensagem de retorno é representada por uma seta tracejada.

- **Mensagem Assíncrona:** Diferente da mensagem síncrona, esse tipo de mensagem não precisa de uma resposta, uma linha de vida que comunica uma mensagem síncrona continua sua execução logo após o envio da mensagem. Esse tipo de mensagem é comumente utilizada para representar comunicação de sinais. Em um diagrama de sequência a mensagem assíncrona é representada por uma seta simples.

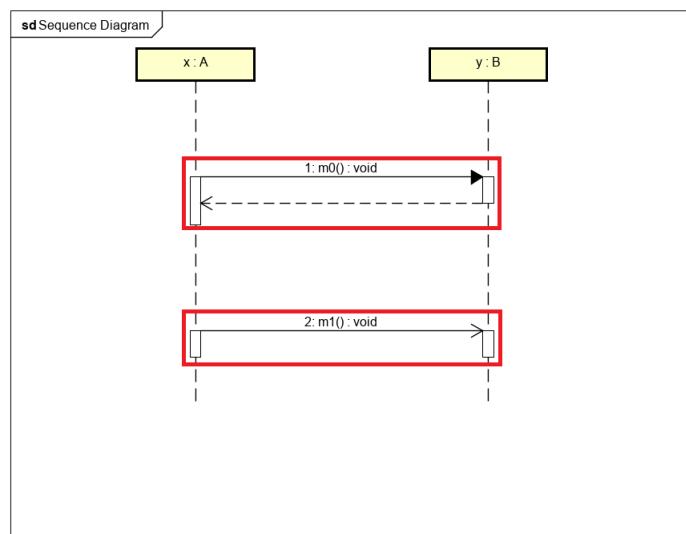

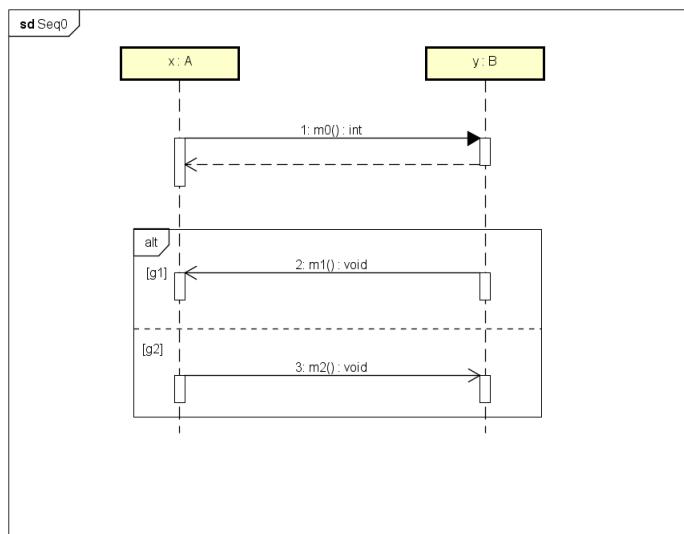

A Figura 3 destaca os diferentes tipos de mensagens presentes em um diagrama de sequência. A mensagem  $m0$  mais acima é síncrona e possui uma mensagem de retorno, enquanto que a mensagem  $m1$  é assíncrona.

Figura 3 – Mensagens em um diagrama de sequência

### 2.1.3 Fragmentos Combinados

Os fragmentos combinados de um diagrama de sequência são uma série de operadores mais complexos que possuem diferentes significados semânticos. Com fragmentos combinados é possível representar operações presentes em linguagens de programação como laços de repetição, operações de escolha e até mesmo paralelismo.

Um fragmento combinado é definido por um operador de interação (*interaction Operator*) e pelos seus respectivos operandos (*interaction Operand*). O operador de

interação define qual o significado semântico do fragmento, define se o fragmento representa uma operação de loop, escolha, paralelismo, dentre outros. Cada fragmento possui um ou mais operandos, esses operandos são contêineres que agrupam interações que representam um cenário presente no fragmento.

A linguagem UML possui uma grande quantidade de fragmentos combinados para diagramas de sequência, neste trabalho iremos contemplar apenas os fragmentos relacionados a estruturas de controle, ou seja, fragmentos que alteram diretamente o fluxo de um diagrama de sequência.

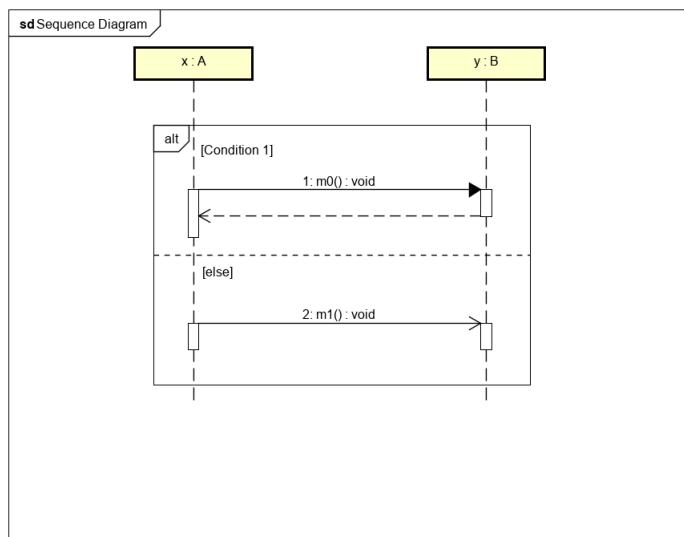

#### 2.1.3.1 Alternative - alt

O fragmento **alt** representa uma operação de escolha ou alternativas de comportamento. Nesse fragmento cada comportamento possível é representado por um operando de interação, tais operandos estão relacionados a uma guarda que representa a condição necessária para que o operando seja executado, em um **alt** apenas um operando pode ser escolhido. O **alt** possui significado semântico similar ao operador *if/else* presente em linguagens de programação.

Figura 4 – Fragmento alt

A Figura 4 representa um fragmento **alt** com apenas dois operandos, sendo um deles relacionado à guarda *else*. Um operando com guarda *else* só será executado caso todos os operandos definidos anteriormente tiverem guardas avaliadas como falso, além disso, caso um operando possua uma guarda vazia a mesma será sempre avaliada como verdadeira.

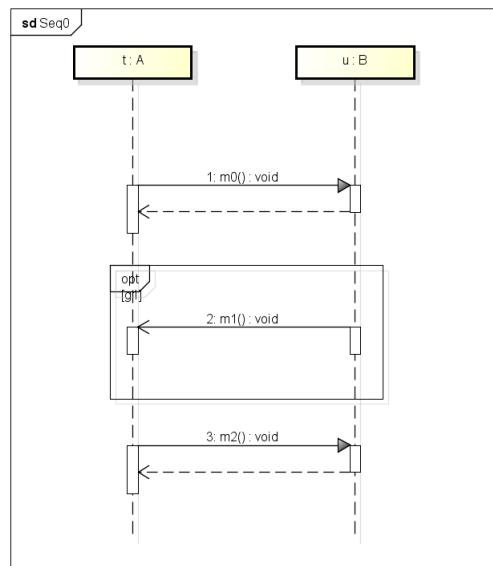

### 2.1.3.2 Option - opt

O fragmento **opt** é muito parecido com o **alt**, o que os diferencia é a quantidade alternativas de comportamentos, enquanto o **alt** deve conter dois ou mais operandos, o **opt** possui apenas um. O **opt** possui o mesmo significado semântico que um operador *if* presente em linguagens de programação, e no contexto do UML possui o mesmo significado semântico que um **alt** com apenas um operando não vazio. A Figura 5 representa um fragmento **opt** que executa a mensagem *m0* caso sua guarda seja avaliada como verdadeira.

Figura 5 – Fragmento opt

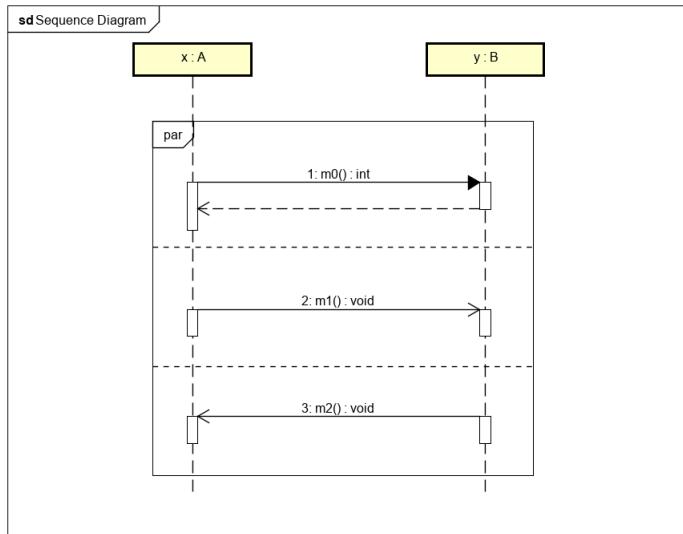

### 2.1.3.3 Parallel - par

O fragmento **parallel** representa a execução paralela de comportamentos. Nesse fragmento cada operando representa um fluxo do paralelismo, ou seja, todos os operandos estão em paralelo e podem ser executados em qualquer ordem. Apesar da ordem de execução dos operandos ser variável, o conteúdo de cada operando ainda deve seguir a ordem de execução que foi definida. O **par** pode ser utilizado para representar uma série de operações independentes que devem ser realizadas mas que não se restrigem a uma ordem de execução específica.

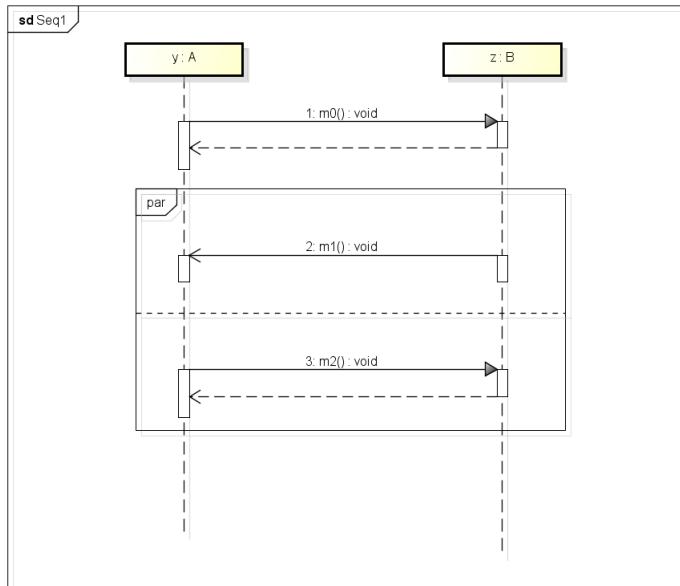

A Figura 6 representa um fragmento **par** com três operandos, cada um desses operandos será executado independentemente de forma paralela.

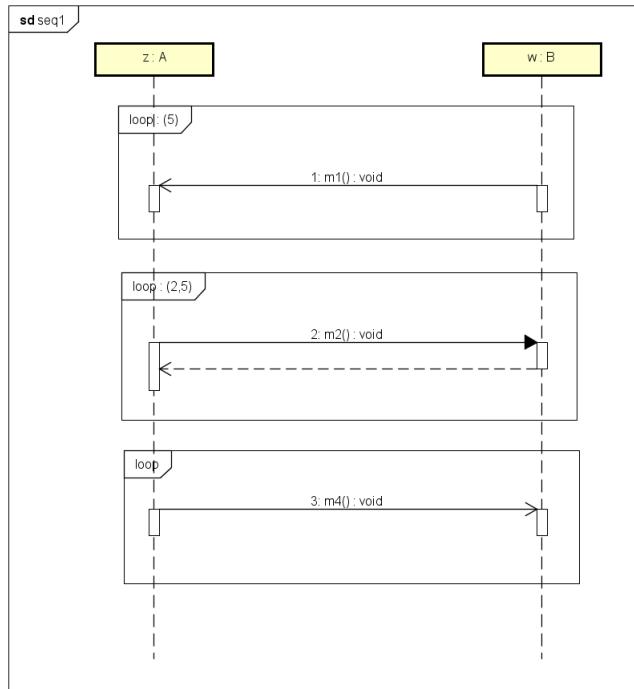

### 2.1.3.4 Loop - loop

O fragmento **loop** representa um loop de repetição. Esse fragmento possui apenas um operando que será repetido um número de vezes. Uma das peculiaridades do

Figura 6 – Fragmento par

*loop* é a forma de limitar seu número de iterações, segundo a ([UML, 2015](#)), os limites do loop podem ser definidos da seguinte forma:

$$loop(min - int[, max - int])$$

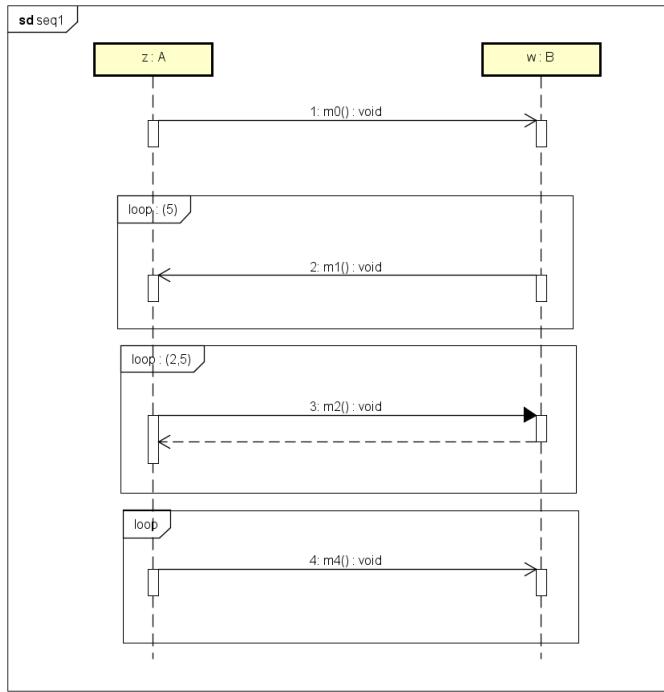

Onde *min-int* representa um limite inferior de iterações e *max-int* representa o limite superior de iterações. Dada essa definição, é possível identificar três formatos distintos de loop:

- **Loop sem limite definido:** Caso não sejam especificados *min-int* e *max-int*, o loop será considerado como infinito. No diagrama ele será representado como *loop* sem nenhum parêntese ou parâmetro.

- **Loop com apenas um limite definido:** Caso o loop só possua um limite definido, apenas o limite inferior será considerado, ou seja, o limite vai representar o número exato de repetições do loop. No diagrama esse tipo de loop será representado como *loop(x)* onde *x* é um número inteiro.

- **Loop com dois limites definidos:** Caso o loop possua limite inferior e superior definidos ele será repetido pelo menos o número de vezes definido no limite inferior, e no máximo o número de vezes definido no limite superior. No diagrama esse tipo de loop vai ser representado por *loop(x, y)* onde *x* e *y* são números inteiros.

A Figura 7 ilustra um diagrama com os diferentes tipos de fragmento *loop*.

Figura 7 – Diagrama com fragmentos loop

## 2.2 CSP

A linguagem CSP é uma álgebra de processos comumente utilizada para representar sistemas constituídos por componentes que interagem entre si. CSP também pode ser utilizada para representar sistemas concorrentes devido a sua variedade de operadores e os tipos de verificação possíveis de realizar, tais verificações permitem identificar comportamentos como *deadlock*, não-determinismo e *livelock*. Além dessas características, o ferramental existente para a linguagem foi um dos pontos importantes para a sua escolha como domínio semântico para diagramas de sequência. O verificador de modelos FDR é a principal ferramenta da linguagem CSP, com ela é possível verificar diversos tipos de refinamento através de uma interface iterativa. A seguir serão apresentadas as principais características da linguagem CSP.

### 2.2.1 Processos e eventos

Um processo CSP é a unidade básica de descrição de comportamento, ele é definido em termos de eventos ou de outros processos. Eventos por sua vez representam alguma ação existente no processo, como por exemplo a comunicação de algum dado. Processos também podem conter diversos operadores do CSP. Tais operadores possuem diferentes semânticas que podem representar desde operações de escolha até paralelismo de processos.

A linguagem apresenta dois processos básicos, *SKIP* e *STOP*. O processo de

*SKIP* representa um término com sucesso, é um processo que comunica o evento (tick) e termina. Por sua vez o processo *STOP* representa o término abrupto de um processo, ou seja, um *deadlock* canônico.

$$ProcessA = event1 \rightarrow SKIP$$

$$ProcessB = event1 \rightarrow STOP$$

O exemplo acima possui dois processos: *ProcessA* e *ProcessB*, e ambos os processos comunicam um evento *event1*. A principal diferença entre esses processos são suas terminações, o primeiro processo termina com sucesso (*SKIP*) enquanto que o segundo entra em *deadlock* (*STOP*). Por convenção os eventos são representados por letras minúsculas e os processos por letras maiúsculas.

### 2.2.2 Tipos de dados e Canais

Um canal define um conjunto de eventos que podem ser realizados pelos processos. É possível definir um canal que comunica diversos tipos de valores. Os tipos de dados presentes no CSP são similares aos encontrados em linguagem de programação. A linguagem possui os tipos primitivos básicos como inteiros, caracteres e booleanos. Além dos tipos primitivos também é possível definir conjuntos, sequências (listas), tuplas e tipos algébricos. Esses últimos podem compor diversos outros tipos em um só.

$$datatype COM = s \mid r$$

$$channel MSG1 : COM$$

$$channel MSG2 : COM.COM$$

Neste exemplo é definido um tipo algébrico *COM* que é composto pelos elementos "s" e "r". A seguir é definido um canal *MSG1* que comunica *COM*, ou seja, comunica os valores "s" e "r". Os canais podem comunicar a composição de *datatypes*, então neste caso o canal *MSG2* pode comunicar qualquer combinação de dois elementos do *datatype COM*.

Além disso, os canais também podem ser utilizados como mecanismos de sincronização entre processos. Na próxima sub-seção deste capítulo serão vistos os operadores de paralelismo presentes em CSP, lá serão exemplificados os diferentes casos de uso de canais para sincronização de processos. Linguagens de programação modernas como Go ([DONOVAN; KERNIGHAN, 2015](#)) utilizam estrutura de canais similares para sincronização em situações de paralelismo.

### 2.2.3 Operadores

Aqui iremos descrever apenas os operadores utilizados ao longo deste trabalho.

#### 2.2.3.1 Operador prefixo

O operador prefixo é representado por " $\rightarrow$ ". Esse operador é utilizado para modelar comportamento sequencial entre processos e eventos.

$$S = a \rightarrow P$$

Neste exemplo o processo  $S$  espera indefinidamente pelo evento "a" e depois se comporta como o processo  $P$ .

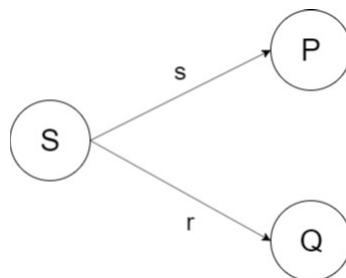

#### 2.2.3.2 Escolha externa

O operador de escolha externa é representado por "[ ]" ou por " $\square$ ". Esse operador é utilizado para representar a decisão do ambiente. Quando dois processos são colocados em escolha externa, apenas um deles será executado enquanto o outro será ignorado.

$$S = (s \rightarrow P) [ ] (r \rightarrow Q)$$

Neste exemplo apenas um dos lados do processo  $S$  será executado. A primeira opção é comunicar o evento  $s$  e então seguir para o processo  $P$ , ou comunicar o evento  $r$  e seguir para o processo  $Q$ . A Figura 8 ilustra o processo  $S$  de forma mais intuitiva.

Figura 8 – Exemplo de escolha externa

#### 2.2.3.3 Composição sequencial

O operador de composição sequencial é representado por ";" . Esse operador é utilizado para compor processos de forma sequêncial. Ao utilizar o operador de composição sequencial entre dois processos estamos sinalizando que o segundo processo será executado assim que o primeiro terminar com sucesso, ou seja, assim que o primeiro processo se comportar como SKIP.

$$S = P ; Q$$

Neste exemplo o processo  $S$  irá iniciar o processo  $P$ , assim que  $P$  terminar sua execução com sucesso o processo  $Q$  será iniciado.

#### 2.2.3.4 Entrelaçamento

O operador de entrelaçamento ou *interleaving*, é representado por “ $|||$ ”. Esse operador é utilizado para realizar a composição paralela de processos. Compor dois processos independentes com *interleaving* significa que esses processos irão executar paralelamente sem sincronizar em nenhum de seus eventos.

$$S = P ||| Q$$

Neste exemplo o processo  $S$  irá iniciar os processos  $P$  e  $Q$ , que serão executados de forma independente sem nenhuma sincronização de eventos.

#### 2.2.3.5 Composição paralela generalizada

O operador de composição paralela generalizada é representado por “[ $X$ ]” onde  $X$  representa um conjunto de eventos. Compor dois processos com esse operador significa que esses processos irão executar paralelamente sincronizando nos eventos do conjunto  $X$ .

$$S = P [ |\{s, x, r\}| ] Q$$

Neste exemplo o processo  $S$  inicia os processos  $P$  e  $Q$  de forma paralela. Esses processos serão executados paralelamente até que um deles tenha que comunicar algum evento do conjunto de sincronização, nesse caso o conjunto  $\{s, x, r\}$ . Ao atingir um evento de sincronização o processo irá parar e esperar que o outro chegue no mesmo evento, após a sincronização os eventos podem continuar paralelamente até atingir outro evento de sincronização. Eventos fora do conjunto de sincronização são livres para serem comunicados.

#### 2.2.3.6 Composição paralela alfabetizada

O operador de composição paralela alfabetizada é representado por “[ $X \parallel Y$ ]” onde  $X$  e  $Y$  representam conjuntos de eventos. Compor dois processos com esse operador significa que esses processos irão executar paralelamente sincronizando nos eventos comuns de  $X$  e  $Y$ , qualquer evento fora desses conjuntos será bloqueado.

$$S = P [ \{s, x\} \parallel \{x, r\} ] Q$$

Neste exemplo o processo  $S$  inicia os processos  $P$  e  $Q$  de forma paralela. Esses processos comunicam os conjuntos de evento  $\{s, x\}$  e  $\{x, r\}$  respectivamente. Devido à composição paralela alfabetizada, esses processos irão sincronizar na interseção dos seus conjuntos de evento, neste caso irão se sincronizar apenas no evento  $x$ .

#### 2.2.3.7 Esconder

O operador de esconder ou *hiding* é representado por “\”. Esse operador tem a funcionalidade de esconder um conjunto de eventos de um processo, os eventos escondidos não poderão ser observados e não serão considerados em nenhuma verificação.

$$S = (a \rightarrow b \rightarrow c \rightarrow SKIP) \setminus \{b, c\}$$

Neste exemplo o processo  $S$  tem os eventos  $b$  e  $c$  escondidos, tais eventos não poderão ser utilizados em nenhuma verificação com o processo  $S$ .

#### 2.2.4 Modelo Semânticos e Traces

Em CSP, um modelo semântico se refere a uma representação abstrata do comportamento dos processos. Existem diversos modelos semânticos em CSP mas neste trabalho será o usado o modelo de *trace*. Um *trace* nada mais é do que uma sequência de eventos presentes em um processo. Dado um processo  $P$ ,  $Traces(P)$  representa o modelo de traces desse processo, ou seja, representa o conjunto com todas as combinações possíveis de eventos presentes nesse processo.

$$P = x \rightarrow y \rightarrow z \rightarrow STOP$$

$$Traces(P) = \{ \langle \rangle, \langle x \rangle, \langle x, y \rangle, \langle x, y, z \rangle \}$$

Como pode ser visto no exemplo acima, o modelo de *traces* é representado por um conjunto de possíveis eventos de um processo, esse foi um dos principais motivos que influenciaram a utilização da linguagem CSP e especificamente do modelo de *traces* para este trabalho. Quando observamos um diagrama de sequência podemos facilmente identificá-lo como um processo. Suas mensagens representam eventos que devem ser executados em ordem e existem elementos que podem realizar alterações no seu fluxo, esse tipo de comportamento pode ser facilmente modelado no contexto de *traces*.

Os modelos semânticos possibilitam os conceitos de **igualdade** e **refinamento**. Considerando o modelo de *traces*, dado dois processos  $P$  e  $Q$  a noção de **igualdade** entre processo é dada por:

$$P \equiv_T Q$$

$$Traces(P) = Traces(Q)$$

Que pode ser interpretado como:

- $P$  tem os mesmo traces que  $Q$ .

- $P$  é igual a  $Q$  no modelo semântico de traces.

Por sua vez, a noção de **refinamento** é dada por:

$$P \sqsubseteq_T Q$$

$$Traces(Q) \subseteq Traces(P)$$

Que pode ser interpretada como:

- $P$  é refinado por  $Q$  no modelo semântico de traces.

- $Q$  refina  $P$  no modelo semântico de traces.

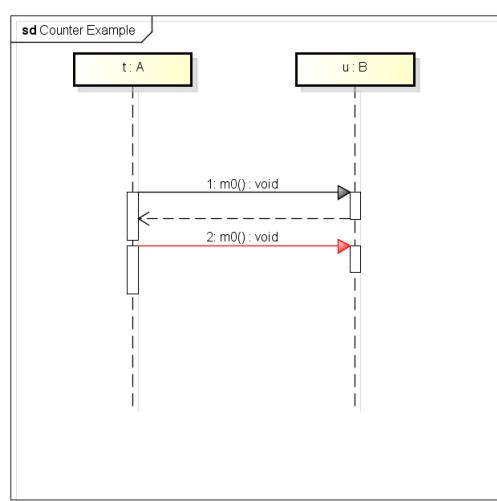

As verificações de refinamento e igualdade nem sempre serão verdadeiros para quaisquer processos  $P$  e  $Q$ . Em casos de falha é possível identificar ao menos um contraexemplo que invalida a verificação. No contexto da verificação de refinamento, um contraexemplo é um *trace* que não cumpre as definições estabelecidas anteriormente, ou seja, não cumpre  $Traces(Q) \subseteq Traces(P)$ .

# 3 Verificação de Refinamento de Diagramas de Sequência

Este capítulo apresenta os detalhes da elaboração e implementação de uma solução para verificação de refinamento de diagramas de sequência UML considerando operadores de controle, aqui serão apresentadas todas as etapas do processo de formalização e verificação de refinamento.

Neste trabalho serão utilizadas as noções de refinamento introduzidas em ([LIMA; IYODA; SAMPAIO, 2016](#)). Nesse trabalho são definidos elementos semânticos importantes para tradução de UML para CSP, utilizaremos a semântica e noções de refinamento desse trabalho relacionado como base ao longo do processo de tradução e verificação, realizando adaptações quando necessário.

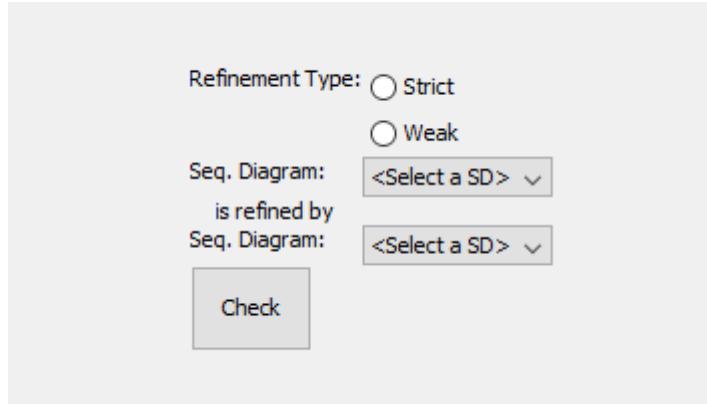

## 3.1 Visão Geral do Processo de Verificação de Refinamento

Assim como foi dito nos capítulos anteriores, a proposta deste trabalho é construir uma ferramenta capaz de realizar verificação de refinamento em diagramas de sequência com suporte a operadores de controle. Tendo isso em mente, o processo de verificação pode ser resumido nas seguintes etapas:

- 1. Criar diagramas de sequência:** Os diagramas de sequência são a base de todo o processo, visto que eles serão o alvo da verificação de refinamentos. A ferramenta Astah-UML ([CHANGE-VISION, 2018](#)) foi escolhida como plataforma alvo do projeto devido à sua grande comunidade, boa usabilidade, versão gratuita para estudantes e ao seu suporte a plugins e API Java.

- 2. Traduzir diagrama de sequência para CSP:** Uma vez que temos uma ferramenta para criar diagramas de sequência agora podemos elaborar uma estratégia de tradução para a linguagem CSP. Para realizar a tradução dos diagramas foi desenvolvido um tradutor na linguagem Java, visto que com Java podemos acessar a API do Astah e consequentemente conseguimos manipular seus diagramas fora do editor da plataforma.

- 3. Verificar Refinamento:** Ao final da etapa de tradução será gerada uma especificação CSP que representa os diagramas que foram traduzidos. Agora que temos uma especificação CSP devidamente criada podemos utilizar a ferramenta FDR

(GIBSON-ROBINSON et al., 2014) para realizar uma verificação de refinamento automatizada.

4. **Detecção de Contraexemplo:** Em caso de falha na verificação de refinamento precisamos identificar qual parte da especificação CSP gerada na etapa de tradução está impossibilitando o refinamento. Para isso utilizamos o FDR para identificar qual o *trace* da especificação causou a falha, esse *trace* é denominado contraexemplo.

5. **Rastreabilidade de Contraexemplo:** Após identificar o contraexemplo na especificação CSP devemos rastrear o evento até a sua implementação nos diagramas de sequência da etapa 1. Tendo identificado o elemento do diagrama relacionado com o *trace* de contraexemplo podemos destacá-lo para que o usuário o identifique facilmente.

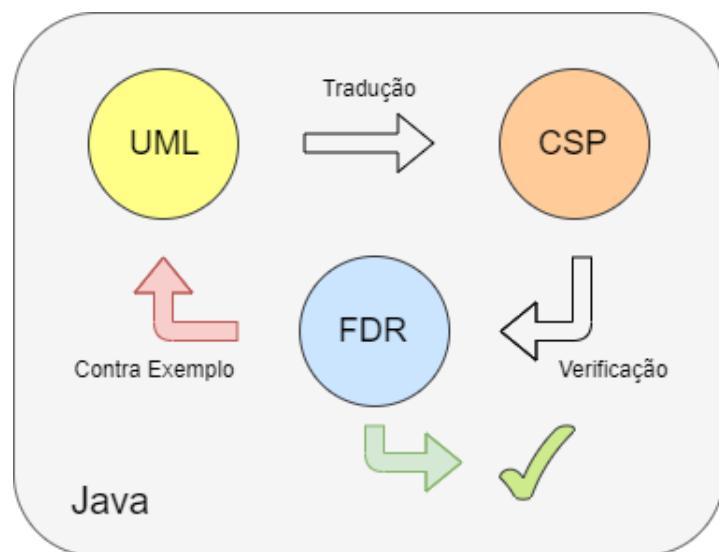

A Figura 9 ilustra as etapas do processo de verificação de refinamento. As seções a seguir descrevem cada etapa do processo de verificação de refinamento em detalhes.

Figura 9 – Visão Geral do Processo de Verificação de Refinamento

### 3.2 Tradução

A etapa de tradução é a base da verificação de refinamento, nessa parte do processo é dada como entrada dois diagramas de sequência que vão gerar duas especificação CSP como saída. Para realizar a etapa de tradução foi desenvolvido um módulo tradutor em Java que utiliza a API da ferramenta Astah para acessar as propriedades dos diagramas de sequência, uma vez que temos acesso a elementos do

diagrama podemos utilizar a semântica de tradução definida em (LIMA; IYODA; SAMPAIO, 2016) para elaborar uma estratégia de tradução.

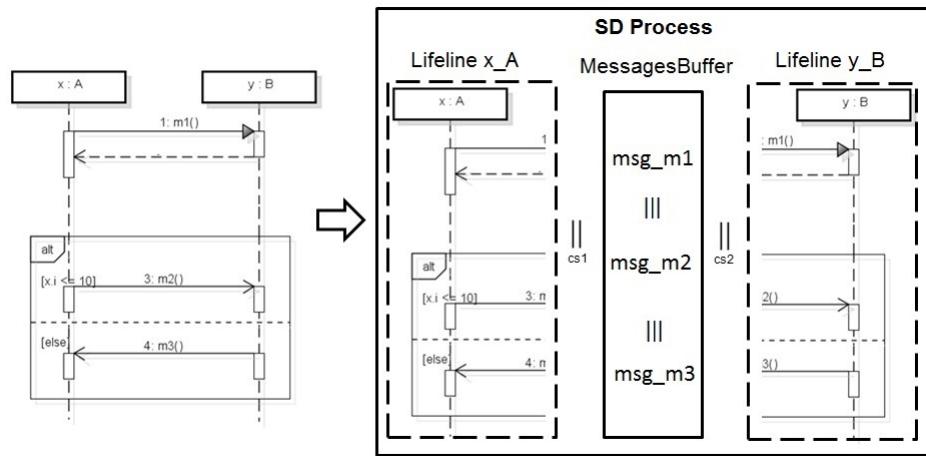

Ao longo da tradução de um diagrama são construídos diversos processos CSP que são compostos paralelamente para formar um processo único que representa todo o diagrama de sequência. Esses processos menores são referentes a elementos do diagrama como as linhas de vida e processos auxiliares para representar o ambiente de trocas de mensagem (*MessagesBuffer*).

Figura 10 – Exemplo do *MessagesBuffer*

A Figura 10 ilustra a utilização de paralelismo na tradução de diagramas de sequência para CSP. Nela podemos observar a presença do *MessagesBuffer*, um processo utilizado para sincronizar a ordem de execução das mensagens, mais detalhes sobre a tradução de mensagens e processos auxiliares como o *MessagesBuffer* serão vistas ao longo do Capítulo.

A seguir vamos apresentar um diagrama de sequência simples e demonstrar todas as etapas do processo de tradução. Para que o tradutor funcione corretamente o diagrama a ser traduzido deve cumprir os seguintes pré-requisitos:

- Todas as linhas de vida devem estar devidamente nomeadas.

- Todas as linhas de vida devem representar instâncias de uma classe previamente definida no projeto do diagrama.

- Todas as mensagens entre linhas de vida devem estar devidamente nomeadas.

- Todas as mensagens entre linhas de vida devem referenciar operações presentes nas classes definidas no projeto do diagrama.

- Todas as mensagens síncronas devem possuir mensagem de retorno.

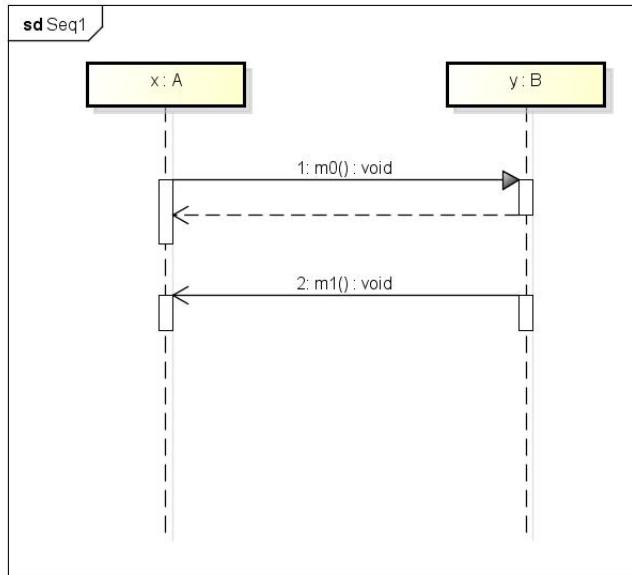

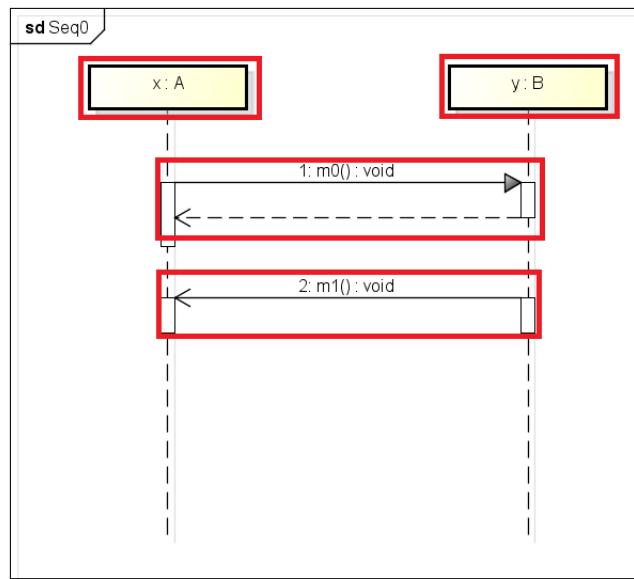

Essas restrições são importantes para garantir um diagrama de sequência bem formado. Tendo em vista esses requisitos, podemos utilizar o diagrama da Figura 11 como exemplo para a tradução.

Figura 11 – Diagrama de sequência para tradução

O diagrama da Figura 11 contém apenas duas linhas de vidas representadas por *x* e *y*, essas linhas de vida são instância das classes A e B respectivamente. O diagrama possui três mensagens, sendo uma mensagem síncrona *m0*, sua mensagem de retorno e uma mensagem assíncrona *m1*. Todos os elementos do diagrama estão devidamente nomeados e, apesar de não ser possível visualizar na imagem, estão associados a uma classe ou operação definida no projeto do diagrama, sendo assim é possível realizar a tradução.

A tradução de diagramas para CSP segue as seguintes etapas:

1. Definição de Tipos de dados

2. Definição de canais de comunicação

3. Construção dos processos de linhas de vida e mensagem

4. Tradução de fragmentos combinados

5. Paralelismo e sincronização de mensagens

### 3.2.1 Definição de tipos de dados

Durante essa etapa o tradutor analisa todas as linhas de vida do diagrama, verificando a quantidade de linhas de vida e suas respectivas classes para que sejam

definidos tipos e subtipos de dados CSP. Como foi visto no Capítulo 2, esses tipos de dados estão associados aos canais de comunicação e aos eventos que eles comunicam. Enquanto verifica todas as linhas de vida do diagrama, o tradutor também verifica as mensagens para que sejam atribuídas aos tipos de dados CSP de suas respectivas linhas de vida e para verificar quais os tipos de parâmetros comunicados no diagrama. A Figura 12 destaca os elementos do diagrama de sequência que são utilizados na definição de tipos de dados.

Figura 12 – Elementos utilizados na definição de tipos de dados

A definição de dados do diagrama em questão é traduzido no trecho da especificação CSP ilustrada pela Figura 13.

```

datatype COM = s | r

datatype ID = lfl1id|lfl2id

datatype ID_SD = sd1id

datatype MSG = m1|m0_I|m0_O

subtype A_SIG = m1

subtype B_OPS = m0_I | m0_O

get_id(m1) = m1

get_id(m0_I) = m0_I

get_id(m0_O) = m0_O

```

Figura 13 – Tipos de dados traduzidos para CSP

Na Figura 13 inicialmente são criados tipos identificadores e modificadores de mensagem. O tipo *COM* é utilizado para representar se uma mensagem está sendo

enviada ou recebida, onde o envio é representado por "s" e o recebimento é representado por "r". Os tipos *ID* e *ID\_SD* provém identificadores únicos para linhas de vida e diagrama de sequência, "*if1id*" representa a primeira linha de vida e "*if2id*" representa a segunda, "*sd1id*" por sua vez identifica o diagrama de sequência como todo.

O diagrama exemplo possui três mensagens, o tipo *MSG* é utilizado para identificá-las. Neste caso como uma das mensagens é síncrona, são criadas dois identificadores, um para representar a mensagem enviada (*m0\_I*), e outro para identificar a mensagem de retorno (*m0\_O*). As mensagens assíncronas são identificadas pelo nome da mensagem no diagrama de sequência, nesse caso apenas a mensagem *m1* é assíncrona.

Durante a identificação dos tipos de mensagens também são criados subtipos que agrupam as mensagens como operações ou sinais. No contexto da tradução de diagramas consideramos as mensagens síncronas como operações e as mensagens assíncronas como sinais, por isso são criados os subtipos como *A\_SIG* e *B\_OPS*. O subtipo *A\_SIG* contém todos os identificadores de mensagens assíncronas enviadas para linhas de vida que são instâncias da classe *A*, o subtipo *B\_OPS* por sua vez contém todos os identificadores relacionados a mensagens síncronas enviadas para linhas de vida que são instâncias da classe *B*.

Ao final das definições de tipos também são criadas funções auxiliares como "*get\_id*" que retornam os identificadores das mensagens do diagrama.

### 3.2.2 Definição de canais de comunicação

Uma vez que os tipos de dados necessários foram definidos, o tradutor pode começar a etapa de definição de canais. Como foi visto no Capítulo 2, os canais em CSP são utilizados para comunicar eventos, tais eventos podem comunicar diferentes dados, no caso dos diagramas de sequência os eventos irão representar a troca de mensagens entre linhas de vida, e os dados que serão comunicados são uma composição dos diferentes tipos de dados traduzidos na etapa anterior. A Figura 14 destaca os elementos do diagrama de sequência que são utilizados na definição dos canais de comunicação.

Figura 14 – Elementos utilizados na definição de canais

Como se pode ver na Figura 15, os canais são compostos por uma composição dos tipos de dados definidos anteriormente. O canal "A\_mSIG" por exemplo vai comunicar todos os eventos relacionados a mensagem assíncronas enviadas para linhas de vida que são instâncias da classe A.

```

channel beginInteraction, endInteraction

channel A_mSIG: COM.ID.ID.A_SIG

channel B_mOP: COM.ID.ID.B_OPS

```

Figura 15 – Canais CSP

Quanto ao formato do evento que será enviado, podemos ver que ele obedece o padrão "COM.ID.ID.A\_SIG", onde "COM" representa se a mensagem está sendo enviada ou recebida, os campos "ID" representam as linhas de vida que estão enviando e recebendo a mensagem, respectivamente, e A\_SIG representa os identificadores das mensagens assíncronas que são enviadas para A. Um evento válido no canal A\_SIG poderia ter o seguinte formato : A\_mSIG.s.lf1id.lf2id.m1.

Além dos canais relacionados às mensagens do diagrama de sequência, também são criados os canais "beginInteraction" e "endInteraction" que serão utilizados posteriormente nas etapas de paralelismo e sincronização para representar o início e fim do fluxo de mensagens, respectivamente. Em diagramas mais complexos também são necessários outros canais auxiliares, como por exemplo para representar guardas em fragmentos combinados.

### 3.2.3 Construção dos processos de linhas de vida e mensagem

Após a construção dos canais de comunicação, o próximo passo do tradutor é criar os processos que vão representar as linhas de vida e as mensagens do diagrama. Para isso o tradutor começa a avaliar as linhas de vida individualmente, percorrendo-as verticalmente de cima para baixo, traduzindo todas as mensagens e fragmentos. Os processos criados são constituídos de eventos que representam as mensagens da linha de vida, todos os eventos são definidos na mesma ordem em que acontecem no diagrama de sequência. A Figura 16 destaca os elementos do diagrama de sequência que são utilizados na definição dos processos de linha de vida.

Figura 16 – Elementos utilizado na definição dos processos de linha de vida

A Figura 17 ilustra a especificação CSP gerada para as linhas de vida do diagrama em questão.

```

Seq0_x_A(sd_id,lf1_id,lf2_id) = (B_mOP.s!lf1_id!lf2_id.m0_I ->

SKIP); (B_mOP.r!lf2_id!lf1_id?out:{x | x <- B_OPS, (get_id(x) == m0_O) } -> SKIP); (A_mSIG.r!lf2_id!lf1_id?signal:{x | x <- A_SIG, (get_id(x) == m1) } -> SKIP)

Seq0_y_B(sd_id,lf1_id,lf2_id) = (B_mOP.r!lf1_id!lf2_id?oper:{x | x <- B_OPS, (get_id(x) == m0_I) } -> SKIP); (B_mOP.s!lf2_id!lf1_id.m0_O -> SKIP); (A_mSIG.s!lf2_id!lf1_id.m1 -> SKIP)

```

Figura 17 – Processos de linhas de vida em CSP

Os processos das linhas de vida são identificados pelo nome do diagrama, nome da instância da linha de vida e pela classe da linha de vida, no exemplo utilizado

o diagrama é identificado por “Seq0”, as instâncias das linhas de vida são identificadas por “x” e “y” e as classes por “A” e “B”. Cada processo de linha de vida contém todos os eventos de envio e recebimento de mensagens na mesma ordem descrita no diagrama.

Tomando como exemplo o processo “Seq0\_x\_A”, podemos observar que esse processo recebe três parâmetros. Um dos parâmetros é o identificador do diagrama de sequência e os outros dois representam os identificadores das linhas de vida que interagem ao longo do processo, nesse caso como as mensagens comunicadas por esse processo só estão relacionadas a duas linhas de vida, só foram necessários dois parâmetros. A utilização de parâmetros permite a execução de mais de uma instância do mesmo diagrama na especificação CSP gerada.

A tradução das mensagens é feita através da composição de canais de comunicação, assim como visto na Seção 3.2.2. Ainda considerando o processo “Seq0\_x\_A”, podemos observar que nele são comunicados uma série de eventos de mensagens. Inicialmente é comunicada a mensagem  $m0$  e o recebimento de sua respectiva mensagem de retorno, seguido do recebimento da mensagem assíncrona  $m1$ .

Observando o último campo do primeiro evento de mensagem podemos ver o identificador “ $m0\_I$ ”, a terminação “\_I” representa que o evento é referente a uma mensagem síncrona, neste caso a mensagem “ $m0$ ” do diagrama exemplo. Similarmente, um dos eventos do mesmo processo possui um identificador com terminação “\_0”, essa terminação também está presente na tradução de mensagens síncronas mas é utilizado apenas em eventos relacionados a mensagens de retorno, nesse caso o retorno da mensagem “ $m0$ ”. As mensagens assíncronas não possuem nenhuma peculiaridade e são traduzidas sem nenhuma modificação em seus identificadores assim como exemplificado nas Seções anteriores.

Além de definir processos para as linhas de vida, essa etapa da tradução também cria um processo para cada mensagem do diagrama, esses processos são criados para que possam ser utilizados nas etapas de paralelismo e sincronização. A Figura 18 representa os processos CSP de todas as mensagens do diagrama exemplo.

Os nomes dos processos das mensagens possuem identificadores das instâncias e classes das linhas de vida que comunicam a mensagem, assim como o nome do diagrama. Considerando o processo “Seq0\_x\_A\_y\_B\_m0” da Figura 18 temos “Seq0” como identificador do diagrama, “x\_A” como identificador da linha de vida origem da mensagem, “y\_B” como identificador na linha de vida destino da mensagem e “m0” como identificador da mensagem. Ainda observando a Figura 18 podemos identificar que cada processo possui parâmetros similares aos processos de linha de vida, e que eles comunicam os eventos de envio e recebimento de sua mensagem associada.

```

Seq0_x_A_y_B_m0(sd_id,lf1_id,lf2_id) = B_mOP.s.lf1_id.lf2_id?x:(x |

x<-B_OPS,get_id(x) == m0_I} -> B_mOP.r.lf1_id.lf2_id!x ->

Seq1_x_A_y_B_m0(sd_id,lf1_id,lf2_id)

Seq0_y_B_x_A_m1(sd_id,lf2_id,lf1_id) = A_mSIG.s.lf2_id.lf1_id?x:(x |

x<-A_SIG,get_id(x) == m1} -> A_mSIG.r.lf2_id.lf1_id!x ->

Seq1_y_B_x_A_m1(sd_id,lf2_id,lf1_id)

Seq0_y_B_x_A_m0_r(sd_id,lf2_id,lf1_id) = B_mOP.s.lf2_id.lf1_id?x:(x |

x<-B_OPS,get_id(x) == m0_O} -> B_mOP.r.lf2_id.lf1_id!x ->

Seq1_y_B_x_A_m0_r(sd_id,lf2_id,lf1_id)

```

Figura 18 – Processos de mensagens em CSP

Diferentemente dos processos de linha de vida que terminavam com um *SKIP*, os processos da mensagem reiniciam após a comunicação de seus eventos, isso acontece porque esses processos só serão utilizados como auxiliares na etapa de paralelismo e sincronização.

Esses processos de mensagem serão utilizados posteriormente na etapa de paralelismo e sincronização, mais especificamente no processo *MessagesBuffer*. Esse processo auxiliar realiza a composição paralela dos processos de mensagens do diagrama e tem o intuito de possibilitar a execução ordenada dos eventos que compõem os processos de mensagens.

A Figura 19 representa o processo *MessagesBuffer* gerado para o diagrama exemplo da Figura 16. Nesse processo podemos observar a composição paralela dos processos de mensagens através do operador de entrelaçamento (*interleaving*), o uso desse operador implica no paralelismo completo dos processos associados.

```

Seq0_MessagesBuffer(sd_id,lf1_id,lf2_id) =

(Seq0_x_A_y_B_m0(sd_id,lf1_id,lf2_id) |||

Seq0_y_B_x_A_m0_r(sd_id,lf2_id,lf1_id) |||

Seq0_y_B_x_A_m1(sd_id,lf2_id,lf1_id)) /\endInteraction ->

SKIP

```

Figura 19 – Processo *MessagesBuffer*

### 3.3 Tradução de Fragmentos Combinados

Ainda dentro da etapa de tradução de linhas de vida e mensagens está a tradução de fragmentos combinados. Alguns diagramas mais complexos possuem frag-

mentos combinados, esses elementos do diagrama são complexos o suficiente para precisarem de módulos tradutores específicos. O estado atual da ferramenta dá suporte a quatro fragmentos combinados, sendo eles: *alt*, *opt*, *par* e *loop*.

### 3.3.1 Tradução do fragmento *alt*

Como foi citado no Capítulo 2, o fragmento *alt* representa uma escolha para diferentes alternativas de comportamento. A Figura 20 ilustra um diagrama com um fragmento *alt*, no exemplo em questão o fragmento possui apenas duas alternativas, ou seja, dois operandos e duas guardas. O desafio em traduzir o fragmento *alt* está na avaliação das guardas e na construção de um processo que represente diferentes possibilidades de fluxo.

Figura 20 – Diagrama com fragmento *alt*

O primeiro passo para possibilitar a tradução do *alt* é definir canais extras que representam as avaliações das guardas presentes no fragmento, para o exemplo em questão o seguinte canal será criado:

*channel alt1 : Bool.Bool*

As guardas só podem ser avaliadas como *true* ou *false*, para isso são criados canais para cada *alt* e nele são adicionados um número de parâmetros booleanos equivalente ao número de guardas presentes no fragmento. Dessa forma é possível representar as diferentes possibilidades de fluxo dentro de um *alt*. No estado atual da ferramenta as guardas são definidas de forma abstrata utilizando apenas um identificador genérico ao invés de uma condição real. Isso acontece pois a ferramenta ainda não possui integração com uma semântica de definição de classes e parâmetros, essa é uma melhoria prevista para trabalhos futuros.

Após a definição dos canais auxiliares é possível construir um processo que represente o fragmento *alt*, para isso é utilizado o operador de escolha externa do CSP. A Figura 21 ilustra um processo gerado após a tradução do fragmento *alt* considerando a linha de vida da classe A presente na Figura 20. Na definição do processos são criados fluxos de execução correspondentes a cada um dos operandos presentes no fragmento, esses fluxos são compostos com o operador de escolha externa permitindo que apenas um seja executado.

```

alt1?g1?g2 -> (g1 & (A_mSIG.r!lf2_id!lf1_id?signal:{x | x <-

A_SIG, (get_id(x) == m1)} -> SKIP)

[]

g2 & (B_mSIG.s!lf1_id!lf2_id.m2 -> SKIP)

[]

(g1 == false and g2 == false) & SKIP)

```

Figura 21 – Tradução do fragmento *alt*

Na Figura 21 podemos observar as duas guardas *g1* e *g2* que foram utilizadas no diagrama exemplo, contudo essa não é a única forma de utilizar guardas no fragmento *alt*. Caso um operando não possua guarda definida, a mesma será implicitamente avaliada como verdadeira, outra forma de criar um operando que sempre terá uma guarda verdadeira é atribuindo o valor *else* à guarda.

Na prática, a tradução de um fragmento vai ser inserida no processo de cada linha de vida que é cruzada pelo mesmo, então a tradução das linhas de vida do exemplo em questão será representado pelo trecho ilustrado na Figura 22.

### 3.3.2 Tradução do fragmento *opt*

O fragmento *opt* possui um comportamento similar ao *alt*, porém se diferencia na quantidade de operandos, essa similaridade permite que a tradução do *opt* siga a mesma lógica do *alt*. A Figura 23 representa um diagrama de sequência com um fragmento *opt*.

Assim como na tradução do fragmento *alt*, é necessária a criação de canais extras para representar a avaliação da guarda do único operando do fragmento *opt*. Para o exemplo em questão será criado um canal simples :

*channel opt1 : Bool*

```

Seq0_x_A(sd_id,lf1_id,lf2_id) =(B_mOP.s!lf1_id!lf2_id.m0_I

-> SKIP);(B_mOP.r!lf2_id!lf1_id?out:{x | x

<-B_OPS,(get_id(x) == m0_O)} -> SKIP);

alt1?g1?g2 -> (g1 & (A_mSIG.r!lf2_id!lf1_id?signal:{x | x <-

A_SIG,(get_id(x) == m1)} -> SKIP)

[]

g2 & (B_mSIG.s!lf1_id!lf2_id.m2 -> SKIP)

[]

SKIP)

Seq0_y_B(sd_id,lf1_id,lf2_id)=(B_mOP.r!lf1_id!lf2_id?oper:{x

| x <- B_OPS,(get_id(x) == m0_I)} ->

SKIP);(B_mOP.s!lf2_id!lf1_id.m0_O -> SKIP);

alt1?g1?g2 -> (g1 & (A_mSIG.s!lf2_id!lf1_id.m1 -> SKIP)

[]

g2 & (B_mSIG.r!lf1_id!lf2_id?signal:{x | x <-

B_SIG,(get_id(x) == m2)} -> SKIP)

[]

SKIP)

```

Figura 22 – Tradução de linhas de vida com fragmento *alt*Figura 23 – Diagrama com fragmento *opt*

Diferentemente do *alt* que pode possuir inúmeros operandos, o fragmento *opt* sempre irá possuir apenas um operando, e isso se reflete no seu canal que possui apenas um parâmetro booleano. Outra similaridade em relação ao fragmento *alt* é o processo gerado após a tradução. O fragmento *opt* também requer a utilização do operador de escolha externa, mas o utiliza em apenas uma verificação simples de guarda, assim como mostra a Figura 24.

A tradução das linhas de vida incluindo a tradução do *opt* é representada pela Figura 25.

```

opt1?g1 -> (g1 & (A_mSIG.r!lf2_id!lf1_id?signal:{x | x <-

A_SIG, (get_id(x) == m1)} -> SKIP) [] (g1 == false) & SKIP)

```

Figura 24 – Tradução do fragmento *opt*

```

Seq0_t_A(sd_id,lf1_id,lf2_id) =(B_mOP.s!lf1_id!lf2_id.m0_I

-> SKIP); (B_mOP.r!lf2_id!lf1_id?out:{x | x

<-B_OPS, (get_id(x) == m0_O)} -> SKIP);

opt1?g1 -> (g1 & (A_mSIG.r!lf2_id!lf1_id?signal:{x | x <-

A_SIG, (get_id(x) == m1)} -> SKIP) [] SKIP);

(B_mOP.s!lf1_id!lf2_id.m2_I ->

SKIP); (B_mOP.r!lf2_id!lf1_id?out:{x | x <-B_OPS, (get_id(x)

== m2_O)} -> SKIP)

Seq0_u_B(sd_id,lf1_id,lf2_id)=

(B_mOP.r!lf1_id!lf2_id?oper:{x | x <- B_OPS, (get_id(x) ==

m0_I)} -> SKIP); (B_mOP.s!lf2_id!lf1_id.m0_O -> SKIP);

opt1?g1 -> (g1 & (A_mSIG.s!lf2_id!lf1_id.m1 ->

SKIP) [] SKIP); (B_mOP.r!lf1_id!lf2_id?oper:{x | x <-

B_OPS, (get_id(x) == m2_I)} ->

SKIP); (B_mOP.s!lf2_id!lf1_id.m2_O -> SKIP)

```

Figura 25 – Tradução de linhas de vida com o fragmento *opt*

### 3.3.3 Tradução do fragmento *par*

O fragmento *par* representa a composição paralela de um conjunto de mensagens. A Figura 26 representa um diagrama de sequência com o fragmento *par*, no exemplo em questão apenas duas mensagens estão dentro do fragmento.

Uma das características do fragmento *par* é a ausência de guardas em seus operandos, assim removendo a necessidade de canais auxiliares. A tradução do fragmento *par* consiste na composição paralela de mensagens através do operador de entrelaçamento (*interleaving*), representado por "|||". A Figura 27 representa a tradução do fragmento *par* do exemplo em questão quando é considerada a linha de vida da classe A.

A tradução das linhas de vidas incluindo a tradução do *par* é representada pela Figura 28.

### 3.3.4 Tradução do fragmento *loop*

Dentre os fragmentos suportados pela ferramenta, o *loop* é o mais complexo do ponto de vista do processo de tradução. A sua complexidade se dá pelo compor-

Figura 26 – Tradução do fragmento *par*

```

(A_mSIG.r!lf2_id!lf1_id?signal:{x | x <- A_SIG, (get_id(x) == m1)} -> SKIP

|||

(B_mOP.s!lf1_id!lf2_id.m2_I -> B_mOP.r!lf2_id!lf1_id?out:{x | x <-B_OPS, (get_id(x) == m2_O)} -> SKIP))

```

Figura 27 – Diagrama com fragmento *par*

```

Seq1_y_A(sd_id,lf1_id,lf2_id) =(B_mOP.s!lf1_id!lf2_id.m0_I -> SKIP); (B_mOP.r!lf2_id!lf1_id?out:{x | x <-B_OPS, (get_id(x) == m0_O)} -> SKIP);

(A_mSIG.r!lf2_id!lf1_id?signal:{x | x <- A_SIG, (get_id(x) == m1)} -> SKIP)||| (B_mOP.s!lf1_id!lf2_id.m2_I -> B_mOP.r!lf2_id!lf1_id?out:{x | x <-B_OPS, (get_id(x) == m2_O)} -> SKIP))

Seq1_z_B(sd_id,lf1_id,lf2_id)=(B_mOP.r!lf1_id!lf2_id?oper:{x | x <- B_OPS, (get_id(x) == m0_I)} -> SKIP); (B_mOP.s!lf2_id!lf1_id.m0_O -> SKIP);

(A_mSIG.s!lf2_id!lf1_id.m1 -> SKIP)||| (B_mOP.r!lf1_id!lf2_id?oper:{x | x <- B_OPS, (get_id(x) == m2_I)} -> B_mOP.s!lf2_id!lf1_id.m2_O -> SKIP))

```

Figura 28 – Tradução de linhas de vida com o fragmento *par*

tamento repetitivo e pela variedade de casos possíveis. Assim como citado na Seção 2.1.3.4 do Capítulo 2, o loop pode possuir três formatos segundo a (UML, 2015):

- **Loop sem limite definido**

- **Loop com apenas um limite definido**

- **Loop com dois limites definidos**

Para cobrir todos os casos de tradução vamos considerar o diagrama de sequência da Figura 29.

Figura 29 – Diagrama de sequência com todos os casos de *loop*

Considerando o primeiro *loop* do exemplo, podemos identificar que se encaixa no caso de **loop com apenas um limite definido**, neste caso o limite são 5 repetições. Por definição, cada iteração do *loop* deve executar todas mensagens presentes no interior do fragmento, nesse caso a mensagem assíncrona *m1*, o desafio da tradução do *loop* está em representar todas as iterações em todos os casos possíveis de *loop*.

Para representar o comportamento do *loop* é necessária a criação de processos auxiliares na etapa de tradução. Esses processos auxiliares servem para representar o comportamento de cada fragmento *loop* de cada linha de vida. A Figura 30 ilustra o processo criado para o primeiro *loop* do exemplo.

Note que este processo utiliza uma abordagem baseada em recursão, onde o processo será chamado recursivamente com parâmetros diferentes até atingir a condição de parada e passar a se comportar como *SKIP*.

Agora considerando o segundo fragmento *loop* do exemplo podemos identificar que ele se encaixa no caso de **loop com dois limites definidos**, neste caso os valores

```

seq1_LOOP1_z_A(iter, bound, lf2_id, lf1_id)=if(iter<=bound)

then A_mSIG.r!lf2_id!lf1_id?signal:{x | x <-

A_SIG, (get_id(x) == m1)} ->

seq1_LOOP1_z_A(iter+1,bound,lf2_id,lf1_id) else SKIP

```

Figura 30 – Processo auxiliar do *loop* com um limite

2 e 5 representam respectivamente o limite inferior e superior de iterações. Por definição, esse caso de *loop* deve executar ao menos o número de iterações definidas pelo limite inferior, após realizar o mínimo de repetições o loop pode continuar até o limite superior ou acabar. Para representar esse comportamento foi necessária a criação de dois processos auxiliares:

```

seq1_LOOP2_z_A(iter,bound,maxbound,lf1_id,lf2_id)=

if(iter<=bound) then B_mOP.s!lf1_id!lf2_id.m2_I ->

B_mOP.r!lf2_id!lf1_id?out:{x | x <-B_OPS, (get_id(x) ==

m2_O)} ->

seq1_LOOP2_z_A(iter+1,bound,maxbound,lf1_id,lf2_id) else

seq1_LOOP2_z_Aaux(iter,bound,maxbound,lf1_id,lf2_id)

seq1_LOOP2_z_Aaux(iter,bound,maxbound,lf1_id,lf2_id)=if(iter

<=maxbound) then B_mOP.s!lf1_id!lf2_id.m2_I ->

B_mOP.r!lf2_id!lf1_id?out:{x | x <-B_OPS, (get_id(x) ==

m2_O)} -> seq1_LOOP2_z_Aaux(iter+1,

bound,maxbound,lf1_id,lf2_id) [] SKIP else SKIP

```

Figura 31 – Processo auxiliar do *loop* com dois limites

Note que neste caso o loop também é utilizado de forma recursiva mas muda o seu comportamento após a realização do número mínimo de iterações. Para representar a possibilidade de saída do *loop* foi utilizado o operador de escolha. Adicionalmente a linguagem UML possui um fragmento denominado *break* que pode ser utilizado para quebrar a execução de outro fragmento, devido a limitações técnicas a ferramenta desenvolvida ainda não possui suporte ao fragmento *break*.

Agora para o último caso do fragmento *loop*, o **loop sem limite definido** ou loop infinito. Dentre os três casos esse é o mais simples, só é necessária a criação de um processo simples que comunica o conteúdo do *loop* e reinicia indefinidamente.

Após a definição de todos esses processos auxiliares é possível utilizá-los nos processos de linhas de vida do diagrama, assim como mostra a Figura 33.

```

seq1_LOOP3_z_A(lf1_id,lf2_id)=B_mSIG.s!lf1_id!lf2_id.m4 ->

seq1_LOOP3_z_A(lf1_id,lf2_id)

```

Figura 32 – Processo auxiliar do *loop* infinito

```

seq1_z_A(sd_id,lf1_id,lf2_id)=(B_mSIG.s!lf1_id!lf2_id.m0 ->

SKIP);seq1_LOOP1_z_A(0,5,lf2_id,lf1_id);seq1_LOOP2_z_A(0,2,5

,lf1_id,lf2_id);seq1_LOOP3_z_A(lf1_id,lf2_id)

seq1_w_B(sd_id,lf1_id,lf2_id)=

(B_mSIG.r!lf1_id!lf2_id?signal:{x | x <- B_SIG, (get_id(x) ==

m0)} -> SKIP);seq1_LOOP1_w_B(0,5,lf2_id,lf1_id);

seq1_LOOP2_w_B(0,2,5,lf1_id,lf2_id);

seq1_LOOP3_w_B(lf1_id,lf2_id)

```

Figura 33 – Tradução de linhas de vida com *loop*

### 3.4 Paralelismo e Sincronização